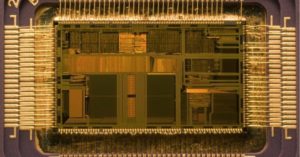

Crack IC ATMEGA168PV Heximal

Crack IC ATMEGA168PV and extract IC firmware out from its flash and eeprom memory, the Heximal can be reprogramme to other blank MCU ATMEGA168PV which will provide the same functions;

Crack IC ATMEGA168PV and extract the firmware out from its flash and eeprom memory, the Heximal can be reprogramme to other blank MCU ATMEGA168PV which will provide the same functions

On the ATMEGA168PV devices, the DRT runs any time the device is powered up. The DRT operates on an internal oscillator. The processor is kept in Reset as long as the DRT is active. The DRT delay allows VDD to rise above VDD min. and for the oscillator to stabilize.

The on-chip DRT keeps the devices in a Reset condition for approximately 18 ms after MCLR has reached a logic high (VIH MCLR) level before hack CPLD EPM240T100A.

Programming GP3/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases.

This allows savings in cost-sensitive and/or space restricted applications, as well as allowing the use of the GP3/MCLR/VPP pin as a general purpose input.

The Device Reset Time delays will vary from chip-to-chip due to VDD, temperature and process variation. See AC parameters for details if restore mcu pic16c54c.

Reset sources are POR, MCLR, WDT time-out and wake-up on pin change. The Watchdog Timer (WDT) is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the internal 4 MHz oscillator. This means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction.

During normal operation or Sleep, a WDT Reset or wake-up Reset, generates a device Reset. The TO bit (STATUS<4>) will be cleared upon a Watchdog Timer Reset. The WDT can be permanently disabled by programming the configuration WDTE as a ‘0’ (see Section 9.1 “Configuration Bits”). Refer to the ATMEGA168PV Programming Specifications to determine how to access the Configuration Word.

Tags: crack ic embedded archive,crack ic embedded code,crack ic embedded content,crack ic embedded data,crack ic embedded eeprom,crack ic embedded file,crack ic embedded firmware,crack ic embedded information,crack ic embedded memory,crack ic embedded program