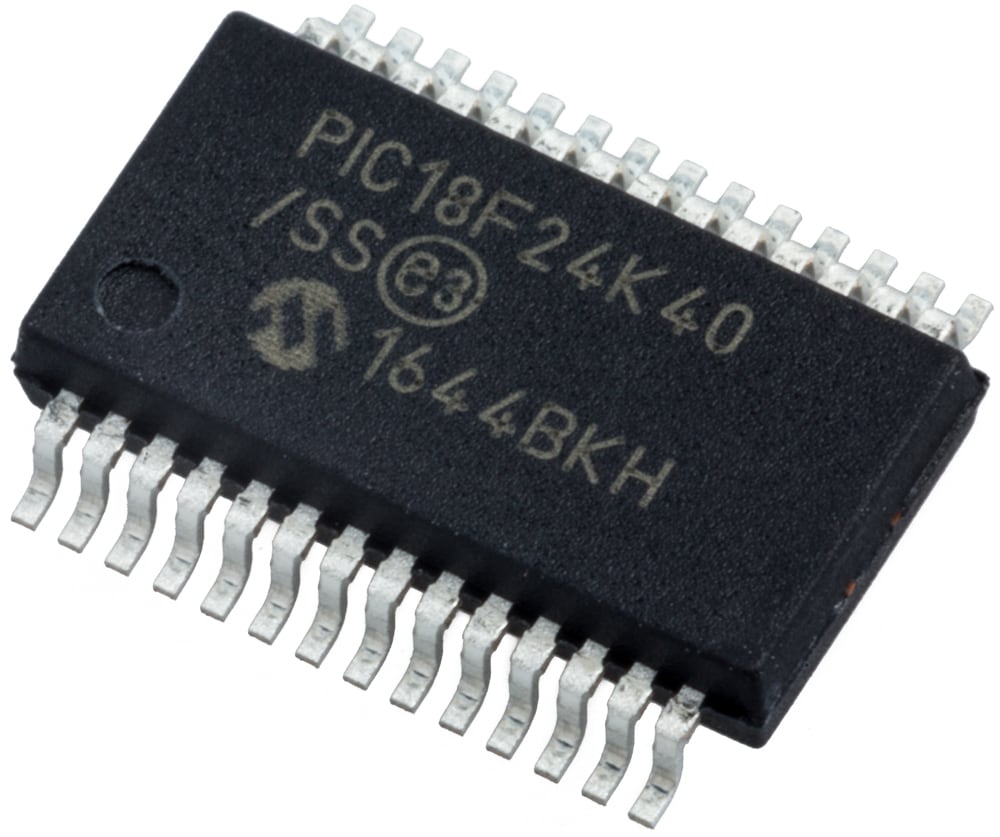

Unlock Microchip PIC18F24K40T Microprocessor Flash Memory

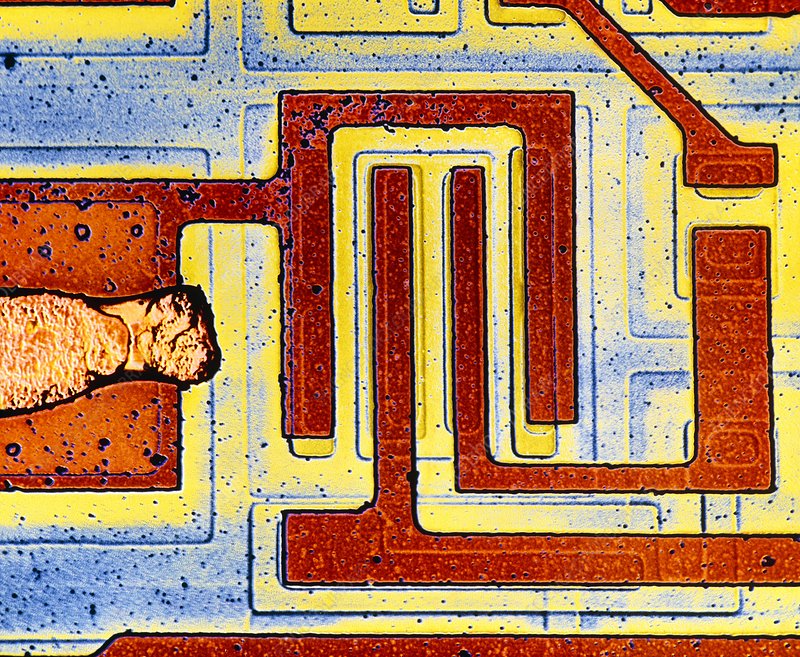

Unlock Microchip PIC18F24K40T Microprocessor Flash Memory is a process of reverse engineer pic18f24k40t microcontroller security fuse bit, and extract embedded firmware from pic18f24k40t MCU;

The LPBOR is controlled by the LPBOREN bit of Configuration Word 2. When the device is erased, the LPBOR module defaults to disabled.

The output of the LPBOR module is a signal indicating whether or not a Reset is to be asserted. This signal is OR’d together with the Reset signal of the BOR module to provide the generic BOR signal when replicating secured mcu pic18f27k40t mcu memory program, which goes to the PCON0 register and to the power control block.

The MCLR is an optional external input that can reset the device. The MCLR function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (see table below). The RMCLR bit in the PCON0 register will be set to ‘0’ if a MCLR has occurred.

When MCLR is disabled, the MCLR becomes input-only and pin functions such as internal weak pull-ups are under software control. The Windowed Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period or window set.

The TO and PD bits in the STATUS register and the RWDT bit are changed to indicate a WDT Reset. The WDTWV bit indicates if the WDT Reset has occurred due to a timeout or a window violation.

Upon exit of Programming mode, the device will behave as if a POR had just occurred to copy microcontroller pic18f27k40 locked flash firmware. The Power-up Timer provides a nominal 66 ms (2048 cycles of LFINTOSC) time out on POR or Brown- out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR. For additional information, refer to Application Note AN607, “Power-up Trouble Shooting” (DS00000607).

Tags: 터놓다 MCU 칩 메모리 소프트웨어 소스 코드,터놓다 마이크로컨트롤러 플래시 메모리 바이너리 파일,터놓다 마이크로컴퓨터 임베디드 펌웨어 데이터,터놓다 마이크로프로세서 플래시 및 eeprom 16진법 프로그램