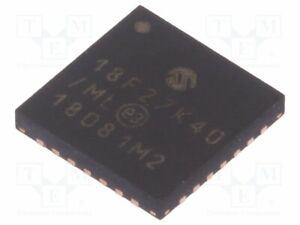

Replicate Secured PIC18F27K40T MCU Memory Program

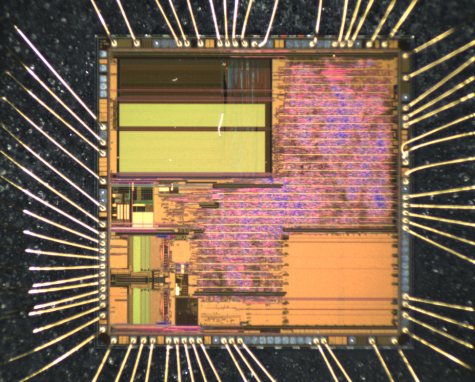

Replicate Secured PIC18F27K40T MCU Memory Program needs to break the protection over microchip controller pic18f27k40t flash memory, and then read secured flash code out from microchip pic18f27k40t microprocessor;

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with these peripherals:

Brown-out Reset (BOR)

Windowed Watchdog Timer (WWDT)

External interrupt pin/Interrupt-On-Change pins

Peripherals that run off external secondary clock source

It is the responsibility of the end user to determine what is acceptable for their application when setting the VREGPM settings in order to ensure operation in Sleep.

The PIC18F24/25K40 devices do not have a configurable Low-Power Sleep mode. PIC18LF24/25K40 devices are unregulated and are always in the lowest power state when in Sleep to unlock secured pic18lf66k80 processor flash memory, with no wake-up time penalty. These devices have a lower maximum VDD and I/O voltage than the PIC18F24/25K40.

When IDLEN is set (IDLEN = 1), the SLEEP instruction will put the device into Idle mode. In Idle mode, the CPU and memory operations are halted, but the peripheral clocks continue to run by . This mode is similar to Doze mode, except that in IDLE both the CPU and PFM are shut off.

IDLE mode ends when an interrupt occurs (even if GIE = 0), but IDLEN is not changed when clone microchip locked pic12f1571 mcu program. The device can re-enter IDLE by executing the SLEEP instruction.

If Recover-On-Interrupt is enabled (ROI = 1), the interrupt that brings the device out of Idle also restores full-speed CPU execution when doze is also enabled.

When in Idle, the WWDT Reset is blocked and will instead wake the device. The WWDT wake-up is not an interrupt, therefore ROI does not apply.

Tags: Kopiuj Kod źródłowy oprogramowania pamięci chipowej MCU,Kopiuj plik binarny pamięci flash mikrokontrolera,Kopiuj program szesnastkowy mikroprocesorowej pamięci flash i eeprom,Kopiuj wbudowane dane oprogramowania układowego mikrokomputera