Microcomputer S3P9234 Memory Program Cloning

The S3P9234 instruction set is designed to support the large register file include the Microcomputer S3P9234 Memory Program Cloning. It includes a full complement of 8- bit arithmetic and logic operations. There are 41 instructions. No special I/O instructions are necessary because I/O control and data registers are mapped directly into the register file. Flexible instructions for bit addressing, rotate, and shift operations complete the powerful data manipulation capabilities of the SAM88RCRI instruction set by Recover MCU.

REGISTER ADDRESSING

To access an individual register, an 8-bit address in the range 0-255 or the 4-bit address of a working register is specified. Paired registers can be used to construct 16-bit program memory or data memory addresses. For detailed information about register addressing for the purpose of Crack MCU ST62T18 Memory, please refer to Section 2, “Address Spaces”.

ADDRESSING MODES

There are six addressing modes: Register (R), Indirect Register (IR), Indexed (X), Direct (DA), Relative (RA), and Immediate (IM). For detailed descriptions of these addressing modes, please refer to Section 3, “Addressing Modes”.

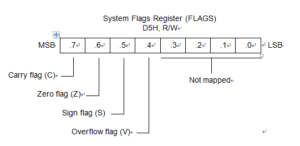

The FLAGS register contains eight bits that describe the current status of CPU operations. Four of these bits, FLAGS.4 – FLAGS.7, can be tested and used with conditional jump instructions to execute the process of Crack IC dsPIC30F6012A Software;

FLAGS register can be set or reset by instructions as long as its outcome does not affect the flags, such as, Load instruction. Logical and Arithmetic instructions such as, AND, OR, XOR, ADD, and SUB can affect the Flags register to facilitate the process of Replicate MC68HC11A8 MCU Memory Program. For example, the AND instruction updates the Zero, Sign and Overflow flags based on the outcome of the AND instruction by Microcomputer S3P9234 Memory Program Cloning. If the AND instruction uses the Flags register as the destination, then simultaneously, two write will occur to the Flags register producing an unpredictable result.