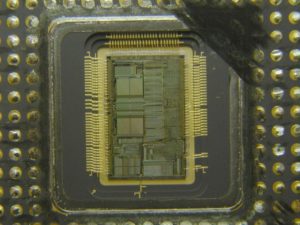

Crack MCU ST62T18 Memory

Acquaintance with the CPU of ST62T18 can provide benefit to Crack MCU ST62T18 Memory, hereby we will introduce the features of the CPU:

The CPU Core of ST6 devices is independent of the I/O or Memory configuration. As such, it may be thought of as an independent central processor communicating with on-chip I/O, Memory and Peripherals via internal address, data, and control buses.

Crack MCU ST62T18 Memory

40 basic instructions

9 main addressing modes Two 8-bit index registers

Two 8-bit short direct registers Low power modes

Maskable hardware interrupts 6-level hardware stack

The ST6 Family CPU core features six registers and three pairs of flags available to the programmer. These are described in the following paragraphs.

Accumulator (A). The accumulator is an 8-bit general purpose register used in all arithmetic cal- culations, logical operations, and data manipulations. The accumulator can be addressed in Data Space as a RAM location at address FFh in order to Break Chip ST62T25 Eeprom Heximal. Thus the ST6 can manipulate the accumulator just like any other register in Data Space.

Index Registers (X, Y). These two registers are used in Indirect addressing mode as pointers to memory locations in Data Space. They can also be accessed in Direct, Short Direct, or Bit Direct addressing modes. They are mapped in Data Space at addresses 80h (X) and 81h (Y) and can be accessed like any other memory location.

Short Direct Registers (V, W). These two registers are used in Short Direct addressing mode. This means that the data stored in V or W can be accessed with a one-byte instruction (four CPU cycles). V and W can also be accessed using Direct and Bit Direct addressing modes from Crack MCU ST62T18 Memory. They are mapped in Data Space at addresses 82h (V) and 83h (W) and can be accessed like any other memory location.

Note: The X and Y registers can also be used as Short Direct registers in the same way as V and W.

Program Counter (PC). The program counter is a 12-bit register which contains the address of the next instruction to be executed by the core when STMelectronics MCU ST62T03 Code Extraction has been completed. This ROM location may be an opcode, an operand, or the address of an operand.