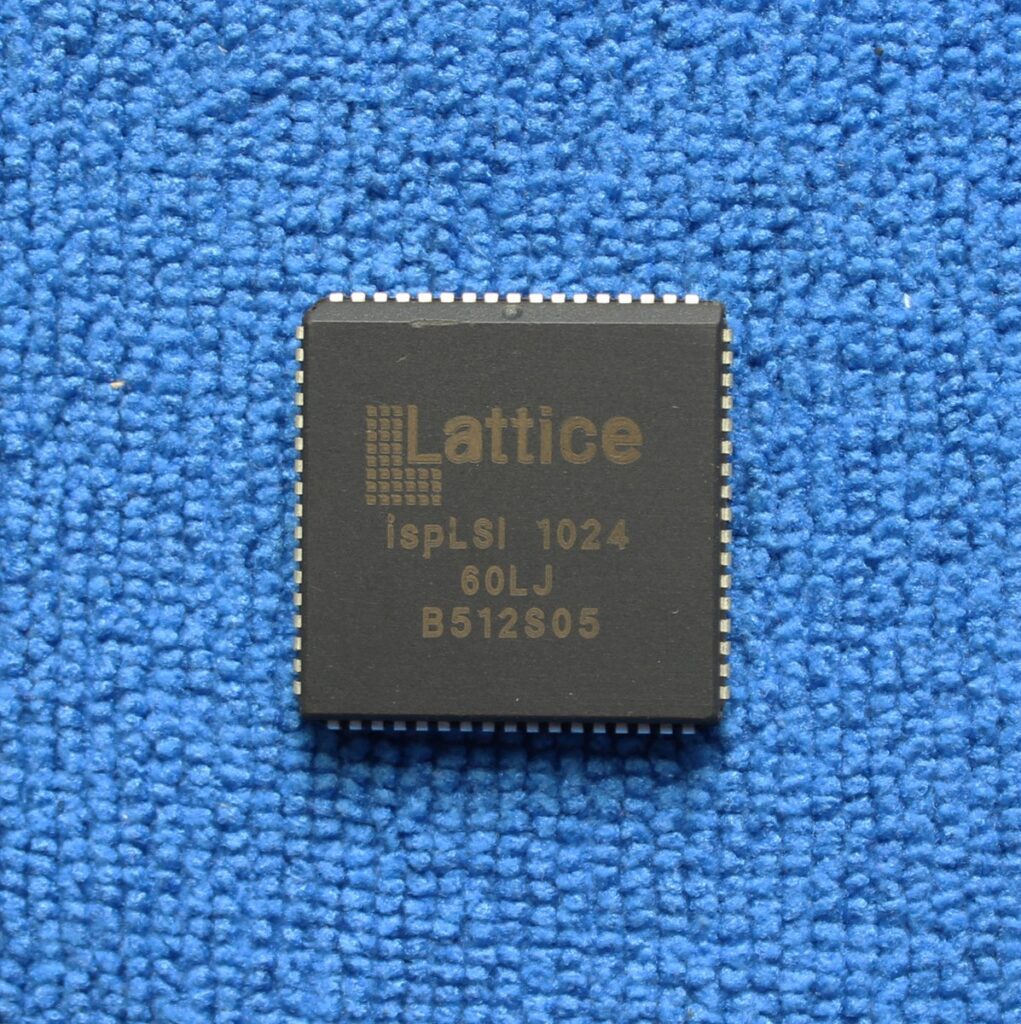

Extract CPLD Lattice ISPLSI1024

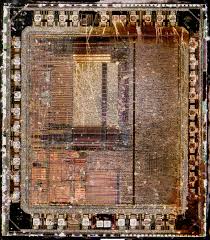

The Lattice ISPLSI1024 is a powerful Complex Programmable Logic Device (CPLD) known for its high-speed logic operations and flexible architecture. Designed for digital control, communication interfaces, and timing-critical systems, this CPLD is often deployed in industrial and defense-grade electronic products. In many scenarios, recovering the embedded logic and configuration from such a secured device becomes essential—whether for system replication, repair, or analysis. For this purpose, the need to extract CPLD Lattice ISPLSI1024 logic configuration becomes crucial.

We can Extract CPLD Lattice ISPLSI1024, please view below chip features for your reference:

— High Speed Global Interconnect

— Wide Input Gating for Fast Counters, State Machines, Address Decoders, etc. Small Logic Block Size for Random Logic

— Electrically Erasable and Reprogrammable

— Non-Volatile

— 100% Tested at Time of Manufacture

— Unused Product Term Shutdown Saves Power

· IN-SYSTEM PROGRAMMABLE

The ISPLSI1024 features a non-volatile flash-based logic array protected by security fuses that lock access to its internal configuration memory. Once the fuse bit is activated, traditional tools are blocked from performing a standard readout of the stored logic file. These fuses are implemented to ensure that the program data cannot be easily copied, decoded, or reverse engineered.

Additionally, the device’s secured nature means that the internal design—typically stored in the form of JEDEC or binary configuration files—is safeguarded from unauthorized duplication. Attempts to clone, replicate, or copy the internal design must therefore rely on advanced techniques to bypass the locked state of the device.

— Increased Manufacturing Yields, Reduced Time-to-Market and Improved Product Quality

— Reprogram Soldered Devices for Faster Prototyping

· OFFERS THE EASE OF USE AND FAST SYSTEM

SPEED OF PLDs WITH THE DENSITY AND FLEXIBILITY

OF FIELD PROGRAMMABLE GATE ARRAYS

— Complete Programmable Device Can Combine Glue

Logic and Structured Designs

— Enhanced Pin Locking Capability

— Four Dedicated Clock Input Pins

— Synchronous and Asynchronous Clocks

— Programmable Output Slew Rate Control to Minimize Switching Noise

— Flexible Pin Placement

— Optimized Global Routing Pool Provides Global Interconnectivity

The process to unlock and extract data from the ISPLSI1024 comes with several technical challenges:

Security Fuse Activation: Once the protection fuse is blown, it disables access to the program memory, blocking standard readout functions.

No JTAG Debugging: Unlike many modern MCUs or microprocessors, CPLDs like the ISPLSI1024 may lack rich debugging interfaces, making standard dump procedures ineffective.

Encrypted Storage: Logic configuration may be encrypted, preventing direct interpretation even if partial data archives are recovered.

Lack of Public Tools: Few commercial tools support restoring data from locked CPLDs, increasing the technical barrier.

We offer a highly specialized service to extract CPLD Lattice ISPLSI1024 logic content through professional, research-backed procedures. Without exposing every proprietary method, our process involves controlled analysis to open the security barrier, retrieve the configuration file, and duplicate or replicate the embedded design as required.

Our methods include advanced reverse engineering workflows, combined with low-level hardware interfacing, to recover the locked content in a non-destructive and reliable manner. In particular, we can:

- Bypass the readout protection implemented by the security fuse

- Remove or neutralize the fuse bit lock without damaging the chip

- Dump the embedded logic file and convert it into usable design formats

- Extensive experience with Lattice CPLDs and other secured chips

- High success rate in restoring, extracting, and replicating embedded logic

- Confidential, legally compliant services for licensed customers

- Ability to decrypt and decode complex binary formats into usable source code or design files

Whether your project involves legacy equipment maintenance, firmware recovery, or system duplication, we provide the perfect solution to extract CPLD Lattice ISPLSI1024 and bring your application back to life—efficiently, accurately, and securely.