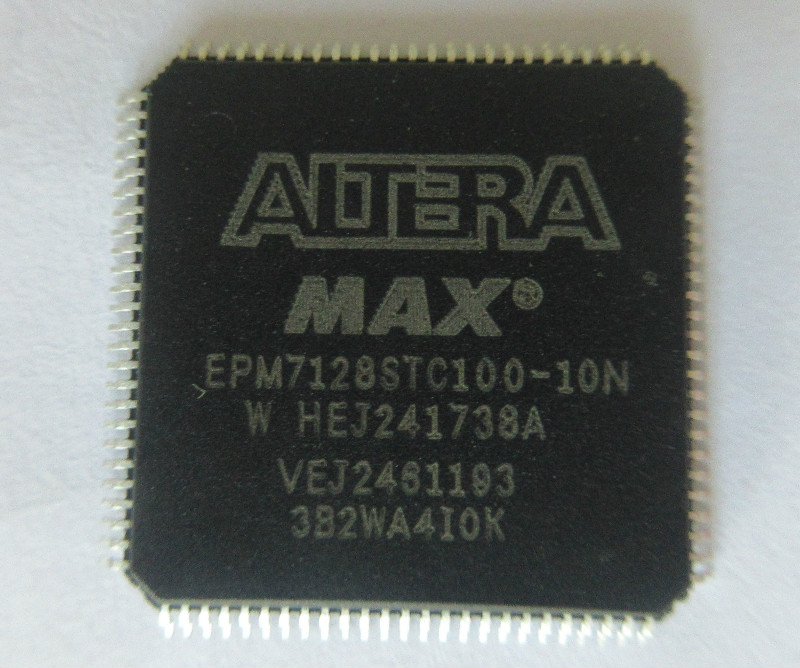

Crack INTEL CPLD EPM7128BTC100-4N

Crack INTEL CPLD EPM7128BTC100-4N is a process to break cpld epm7128btc100 security fuse bit by focus ion beam technique, and copy cpld epm7128btc100 eeprom firmware out from its eeprom memory;

These values are specified under the recommended operating conditions shown in Table 14 on page 28. See Figure 12 for more information on switching waveforms.

These values are specified for a PIA fan-out of one LAB (16 macrocells). For each additional LAB fan-out in these devices, add an additional 0.1 ns to the PIA timing value.

This minimum pulse width for preset and clear applies for both global clear and array controls when unlock cpld epm7128alec programmable logic device. The tLPA parameter must be added to this minimum width if the clear or reset signal incorporates the tLAD parameter into the signal path.

This parameter is measured with a 16-bit loadable, enabled, up/down counter programmed into each LAB when unlock altera cpld epm7128buc processor.

Operating conditions: VCCIO = 2.5 ± 0.2 V for commercial and industrial use.

The tLPA parameter must be added to the tLAD, tLAC, tIC, tEN, tSEXP, tACL, and tCPPW parameters for macrocells running in low-power mode.