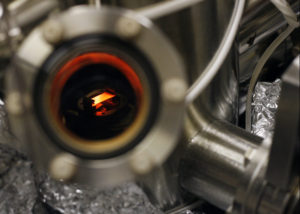

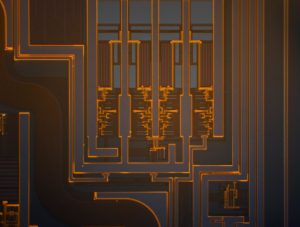

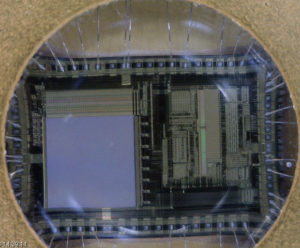

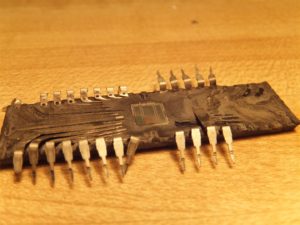

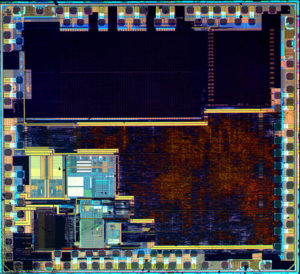

Unlock Microcontroller ATTINY45V Firmware

Unlock Microcontroller ATTINY45V for the purpose of extract IC Firmware from its memory, cracking MCU process normally will need to disable the security fuse bit so the content inside MCU can be dump completely;

Unlock Microcontroller ATTINY45V for the purpose of extract IC Firmware from its memory, cracking MCU process normally will need to disable the security fuse bit so the content inside MCU

· Bit 5:3 – Reserved Bits in MSPI mode

When in MSPI mode, these bits are reserved for future use. For compatibility with future devices, these bits must be written to zero when UCSRnC is written.

· Bit 2 – UDORDn: Data Order

When set to one the LSB of the data word is transmitted first. When set to zero the MSB of the data word is transmitted first. Refer to the Frame Formats section page 4 for details.

· Bit 1 – UCPHAn: Clock Phase

The UCPHAn bit setting determine if data is sampled on the leasing edge (first) or tailing (last) edge of XCKn. Refer to the SPI Data Modes and Timing section page 4 for details.

· Bit 0 – UCPOLn: Clock Polarity

The UCPOLn bit sets the polarity of the XCKn clock. The combination of the UCPOLn and UCPHAn bit settings determine the timing of the data transfer. Refer to the SPI Data Modes and Timing section page 4 for details.

The function and bit description of the baud rate registers in MSPI mode is identical to normal USART operation. See “USART Baud Rate Registers – UBRRLn and UBRRHn” on page 226.

The USART in MSPIM mode is fully compatible with the AVR SPI regarding:

Master mode timing diagram.

The UCPOLn bit functionality is identical to the SPI CPOL bit.

The UCPHAn bit functionality is identical to the SPI CPHA bit.

The UDORDn bit functionality is identical to the SPI DORD bit.

Tags: unlock microcontroller flash archive,unlock microcontroller flash bin,unlock microcontroller flash code,unlock microcontroller flash content,unlock microcontroller flash data,unlock microcontroller flash eeprom,unlock microcontroller flash file,unlock microcontroller flash firmware,unlock microcontroller flash hex,unlock microcontroller flash information,unlock microcontroller flash memory,unlock microcontroller flash program