Unlock Microcontroller ATMEGA169P Heximal

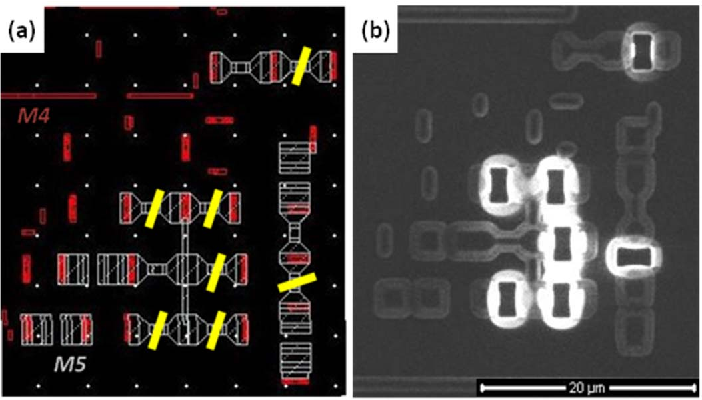

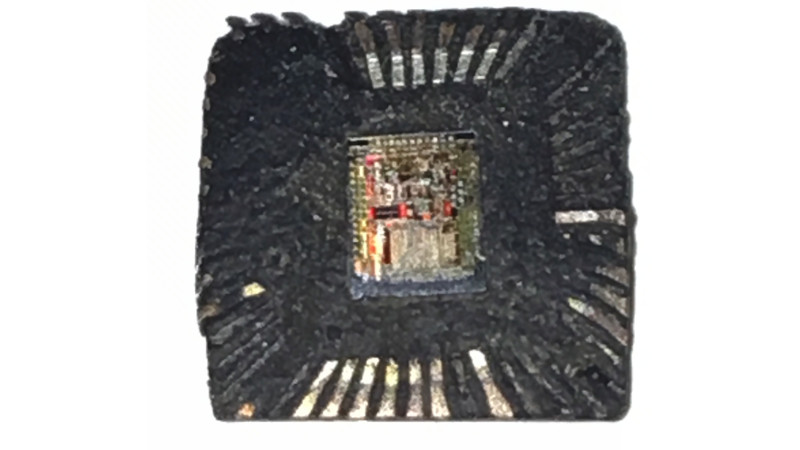

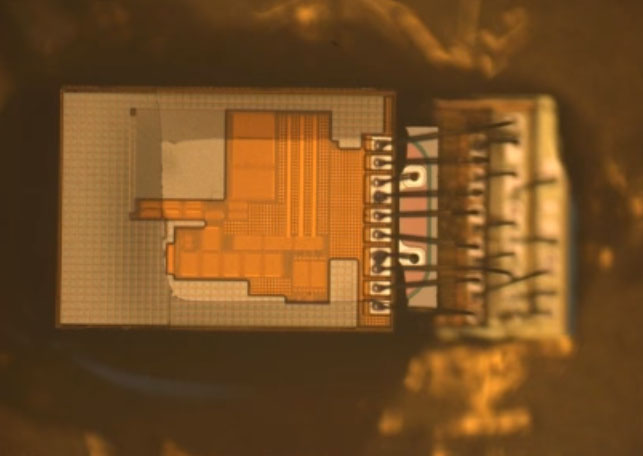

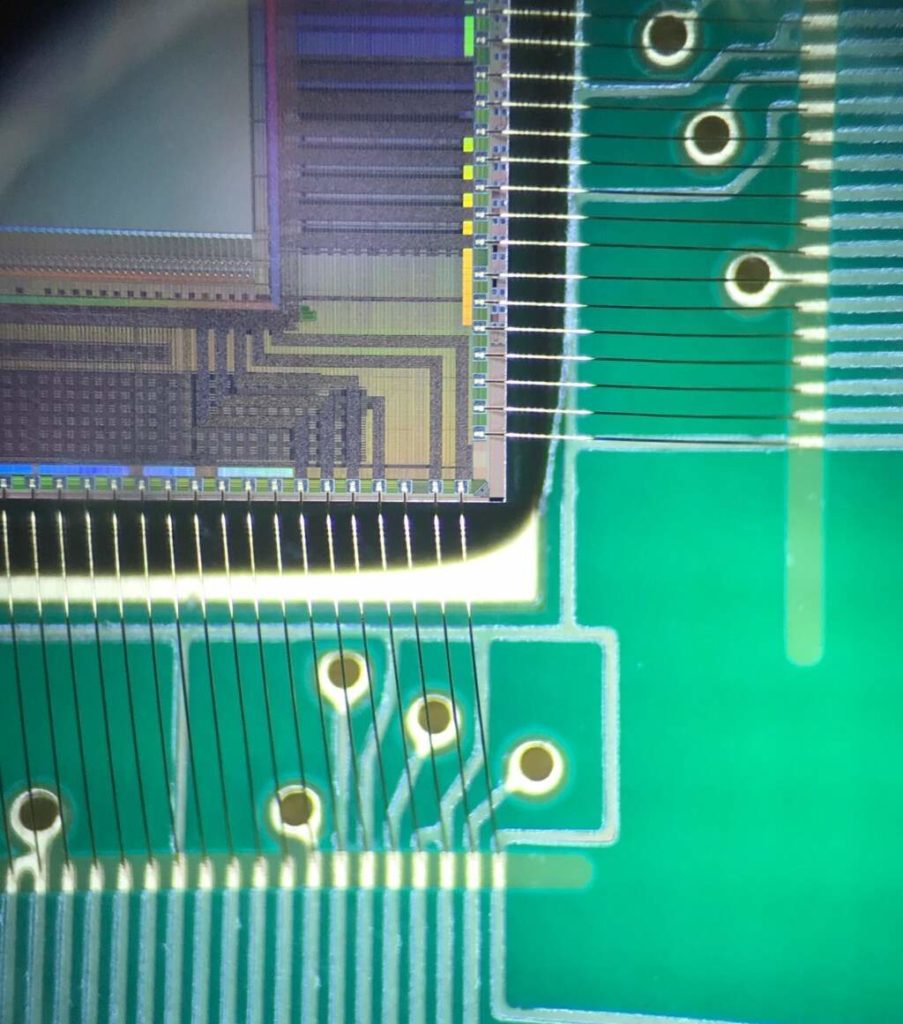

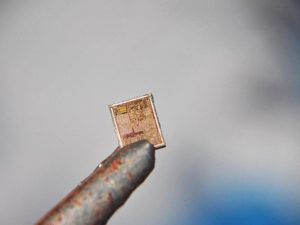

Unlock Microcontroller ATMEGA169P Heximal and release the content of flash and eeprom memory, the process will take 2-3 days since the focus ion beam is going to be required for removing the security fuse bit of MCU recovery;

Unlock Microcontroller ATMEGA169P Heximal and release the content of flash and eeprom memory, the process will take 2-3 days since the focus ion beam is going to be required for removing the security fuse bit of MCU

The TO, PD, GPWUF and CWUF bits in the STATUS register can be tested to determine if a Reset condition has been caused by a power-up condition, a MCLR, Watchdog Timer (WDT) Reset, wake-up on comparator change or wake-up on pin change.

A Brown-out Reset is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown out.

A device may be powered down (Sleep) and later powered up (wake-up from Sleep). The Power-Down mode is entered by executing a SLEEP instruction before crack attiny461 Microcontroller.

If enabled, the Watchdog Timer will be cleared but keeps running, the TO bit (STATUS<4>) is set, the PD bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low or high-impedance).

For lowest current consumption while powered down, the T0CKI input should be at VDD or VSS and the GP3/MCLR/VPP pin must be at a logic high level if MCLR is enabled if read pld palce22v10 device.

The device can wake-up from Sleep through one of the following events:

An external Reset input on GP3/MCLR/VPP pin, when configured as MCLR. A Watchdog Timer time-out Reset (if WDT was enabled).

A change on input pin GP0, GP1 or GP3 when wake-up on change is enabled. wake-up on change is enabled. A comparator output change has occurred when wake-up on comparator change is enabled.

These events cause a device Reset. The TO, PD GPWUF and CWUF bits can be used to determine the cause of device Reset. The TO bit is cleared if a WDT time-out occurred (and caused wake-up).

The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The GPWUF bit indicates a change in state while in Sleep at pins GP0, GP1 or GP3 (since the last file or bit operation on GP port).

The CWUF bit indicates a change in the state while in Sleep of the comparator output.

Tags: unlock microcontroller embedded archive,unlock microcontroller embedded code,unlock microcontroller embedded content,unlock microcontroller embedded data,unlock microcontroller embedded eeprom,unlock microcontroller embedded file,unlock microcontroller embedded firmware,unlock microcontroller embedded information,unlock microcontroller embedded memory,unlock microcontroller embedded program