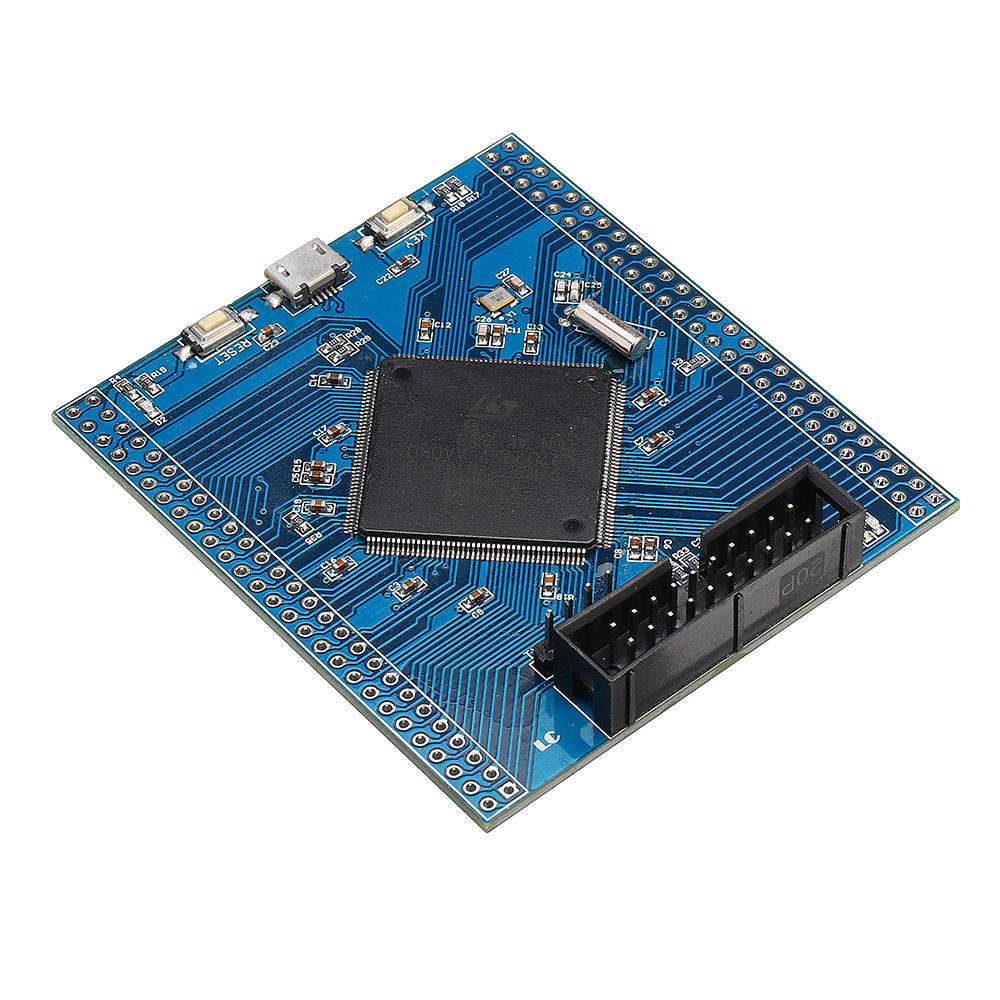

Unlock STM32F205RG Microcontroller Flash Heximal

Unlock STM32F205RG Microcontroller Flash Heximal from its flash is a complete progress to recover embedded firmware from MCU STM32F205RG flash memory, extract source code from microprocessor stm32f205rgt6;

On reset the 16 MHz internal RC oscillator is selected as the default CPU clock. The

16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock is monitored for failure.

If failure is detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails) in order to crack stm32f205rb arm mcu fuse bit.

The advanced clock controller clocks the core and all peripherals using a single crystal or oscillator. In particular, the ethernet and USB OTG FS peripherals can be clocked by the system clock.

Several prescalers and PLLs allow the configuration of the three AHB buses, the high- speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the three AHB buses is 120 MHz and the maximum frequency the high-speed APB domains is 60 MHz when unlock stm32f205rc secured microcontroller flash program. The maximum allowed frequency of the low-speed APB domain is 30 MHz.

The devices embed a dedicate PLL (PLLI2S) that allow them to achieve audio class performance. In this case, the I2S master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.