Recover MC68HC908GT8 Chip Flash Data

The SIM counter is also used for stop mode recovery. The STOP instruction clears the SIM counter. After an interrupt, break, or reset, the SIM senses the state of the short STOP recovery bit, SSREC, in the configuration register 1 (CONFIG1).

If the SSREC bit is a logic 1, then the stop Recover MC68HC908GT8 Chip Flash Data is reduced from the normal delay of 4096 CGMXCLK cycles down to 32 CGMXCLK cycles. This is ideal for applications using canned oscillators that do not require long start-up times from stop mode. External crystal applications should use the full stop recovery time, that is, with SSREC cleared.

External reset has no effect on the SIM counter. (See 8.7.2 Stop Mode for details.) The SIM counter is free-running after all reset states. (See 8.4.2 Active Resets from Internal Sources for counter control and internal reset recovery sequences.)

Normal, sequential program execution can be changed in three different ways:

Interrupts

– Maskable hardware CPU interrupts

– Non-maskable software interrupt instruction (SWI)

Reset

Break interrupts

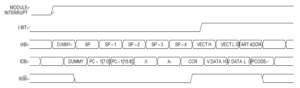

At the beginning of an interrupt to Copy microcontroller, the CPU saves the CPU register contents onto the stack and sets the interrupt mask (I-bit) to prevent additional interrupts to facilitate the process of Motorola MC68HC08AS20 MCU Flash Copying. At the end of an interrupt, the RTI instruction recovers the CPU register contents from the stack so that normal processing can resume. Below Figure shows interrupt entry timing,

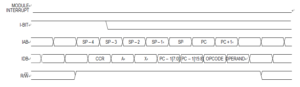

and Below Figure 2 shows interrupt recovery timing.