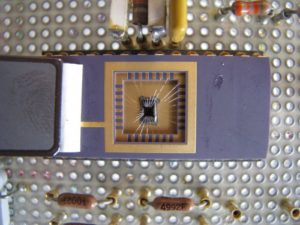

Recover Locked STM32F102RB MCU Program

Recover Locked STM32F102RB MCU Program

Each of the GPIO pins can be configured by software as output by Recovering MCU (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions to manipulate the process of Recover Locked STM32F102RB MCU Program. All GPIOs are high current- capable except for analog inputs.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers by Unlock MCU ATMEGA1284PA Program.

This feature allows the use of a maximum number of peripherals in a given application. Indeed, alternate functions are available not only on the default pins but also on other specific pins onto which they are remappable by Read Microcontroller MCU Texas Instruments MSP430F2121. This has the advantage of making board design and port usage much more flexible.

For details refer to Table 4: STM32F102RB pin definitions; it shows the list of remappable alternate functions and the pins onto which they can be remapped. See the STM32F102RB reference manual for software considerations.

Recover Locked STM32F102RB MCU Program

The 12-bit analog to digital converter has up to 16 external channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs. The ADC can be served by the DMA controller after the process of Unlock NXP P87LPC767 Internal Memory Heximal.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs in order to Clone STM32F102C6 Chip Flash Firmware. The chosen design structure is composed of integrated resistor strings and an amplifier in noninverting configuration.

This dual digital Interface supports the following features:

- l two DAC converters: one for each output channel

- l up to 10-bit output

- l left or right data alignment in 12-bit mode

- l synchronized update capability

- l noise-wave generation

- l triangular-wave generation

- l dual DAC channels’ independent or simultaneous conversions

- l DMA capability for each channel

- l external triggers for conversion

- l input voltage reference VREF+