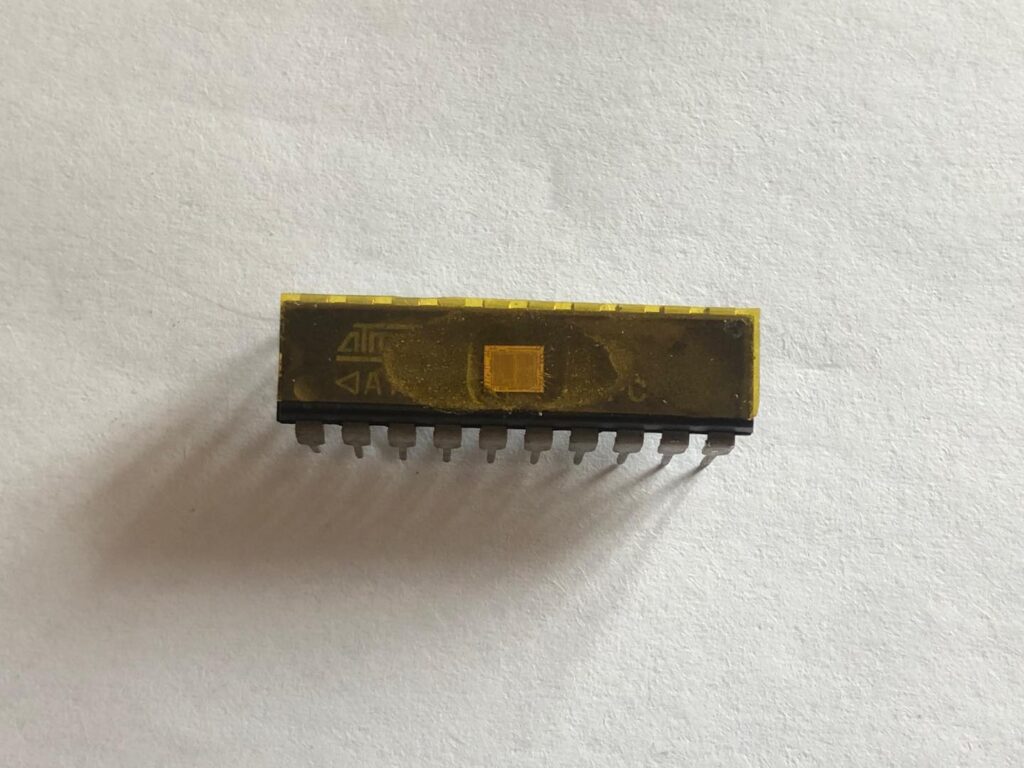

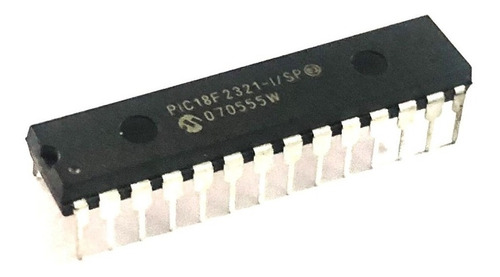

Read Encrypted MCU PIC18F2321T Flash Heximal

Read Encrypted MCU PIC18F2321T Flash Heximal after decrypt microchip pic18f2321 mcu flash memory and eeprom memory, and readout the protected flash binary code from pic18f2321 microcontroller;

After a Start bit, the SPBRG begins counting up using the preselected clock source on the first rising edge of RX. After eight bits on the RX pin, or the fifth rising edge, an accumulated value totaling the proper BRG period is left in the SPBRGH:SPBRG registers.

Once the fifth edge is seen (should correspond to the Stop bit), the ABDEN bit is automatically cleared by cracking pic18f2321 mcu heximal file. While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock will be configured by the BRG16 and BRGH bits.

Independent of the BRG16 bit setting, both the SPBRG and SPBRGH will be used as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes, by checking for 00h in the SPBRGH register.

Refer to Table 16-4 for counter clock rates to the BRG. While the ABD sequence takes place to unlock pic18f4320 microchip processor binary file, the EUSART state machine is held in Idle. The RCIF interrupt is set once the fifth rising edge on RX is detected. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded.