Philip P89C52 Microcontroller Flash Heximal Extraction

Philip P89C52 Microcontroller Flash Heximal Extraction refers to the disable the security fuse bits and then makes it become directly readable status, and then the content from both eeprom and flash can be read.

In below article we will introduce some features for this Microcontroller:

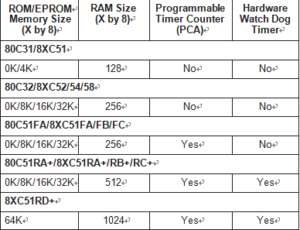

Three different Single-Chip 8-Bit Microcontroller families are presented in this datasheet:

P89C52

For applications requiring 4K ROM/EPROM, see the P89C52 8-bit CMOS (low voltage, low power, and high speed) microcontroller families datasheet. All the families are Single-Chip 8-Bit Microcontrollers manufactured in advanced CMOS process and are derivatives of the 80C51 microcontroller family. All the devices have the same instruction set as the 80C51. These devices provide architectural enhancements that make them applicable in a variety of applications for general control systems.

The ROMless devices, P89C52 can address up to 64K of external memory. All the devices have four 8-bit I/O ports, three 16-bit timer/event counters, a multi-source, four-priority-level, nested interrupt structure, an enhanced UART and on-chip oscillator and timing circuits to recover MCU. For systems that require extra memory capability up to 64k bytes, each can be expanded using standard TTL-compatible memories and logic.

Its added features make it an even more powerful microcontroller for applications that require pulse width modulation, high-speed I/O and up/down counting capabilities such as motor control. It also has a more versatile serial channel that facilitates multiprocessor communications and Restore NXP P89LPC922 Microcontroller Flash Heximal.

- 80C51 Central Processing Unit

- Speed up to 33MHz

- Full static operation

- Operating voltage range: 2.7V to 5.5V @ 16MHz

- Security bits:

- – ROM – 2 bits

- – OTP–EPROM – 3 bits

- Encryption array – 64 bytes

- RAM expandable to 64K bytes

- 4 level priority interrupt

- 6 or7 interrupt sources, depending on device

- Four 8-bit I/O ports

- Full-duplex enhanced UART

- – Framing error detection

- – Automatic address recognition

- Power control modes

- – Clock can be stopped and resumed

- – Idle mode

- – Power down mode

- Programmable clock out

- Second DPTR register

- Asynchronous port reset

Low EMI (inhibit ALE)