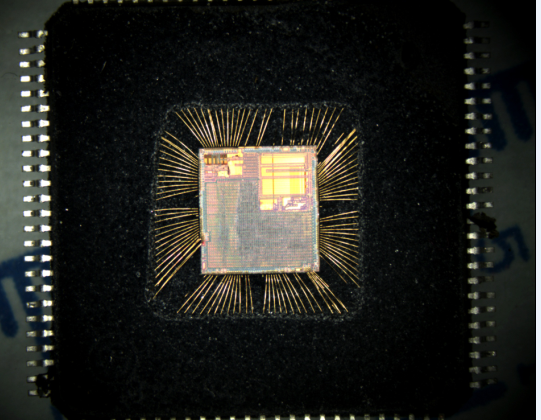

Locked STM32F048G6 Microprocessor Flash Code Copying

Locked STM32F048G6 Microprocessor Flash Code Copying needs to attack readout protection over stm32f048g6 microcontroller, and then extract embedded source code from stm32f048g6 protective mcu;

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines, RTC, I2C1, USART1, USART2, USB, VDDIO2 supply comparator or the CEC. The CEC, USART1 and I2C1 peripherals can be configured to enable the HSI RC oscillator so as to get clock for processing incoming data.

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected when crack stm32f048c6 microcontroller flash, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator.

A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).