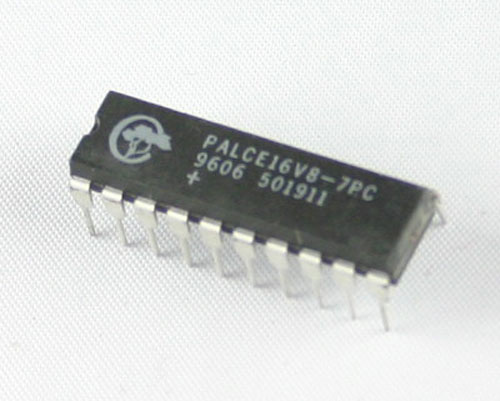

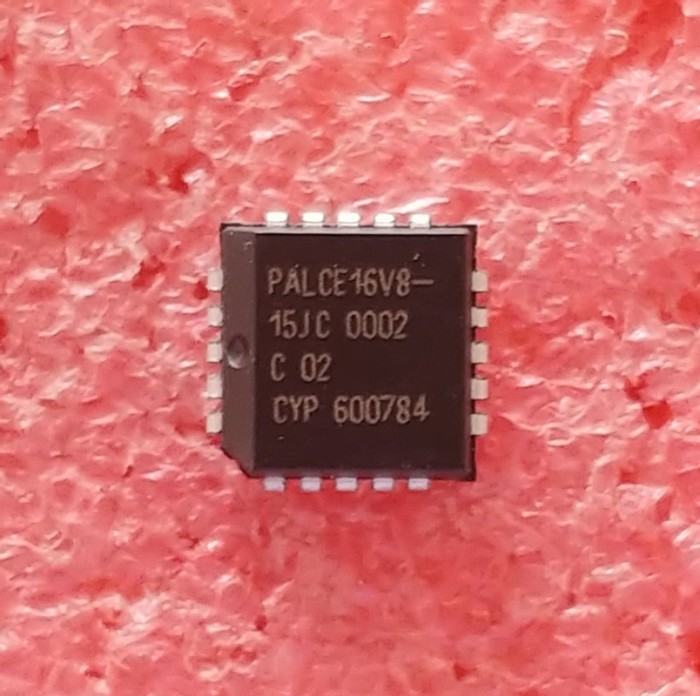

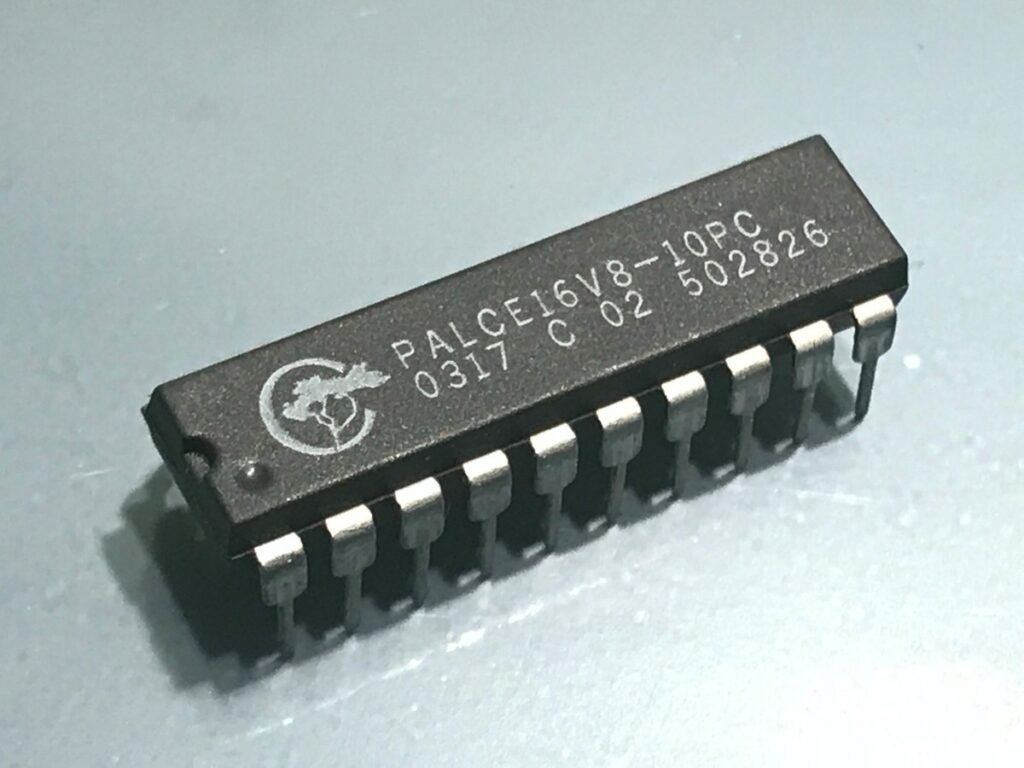

Extract PLD IC PALCE16V8

The PALCE16V8 is a Programmable Logic Device (PLD) from Lattice Semiconductor, widely used in industrial control systems, legacy hardware, and custom digital logic applications. It offers a flexible and customizable architecture, allowing developers to implement specific logic functions directly into the hardware. When the original programming files are lost or the chip is secured, the ability to extract PLD IC PALCE16V8 logic becomes essential for hardware restoration, compatibility upgrades, or system cloning.

What Makes the PALCE16V8 Unique

Unlike traditional microcontrollers (MCUs) or microprocessors, the PALCE16V8 is a purely combinational or sequential logic device. It doesn’t contain firmware, flash, or EEPROM in the typical sense but rather a matrix of programmable fuses or memory cells that define its logic configuration. Once programmed, especially in protected or locked mode, the internal structure becomes inaccessible through conventional means, making data recovery a highly specialized task.

Despite its simplicity in architecture compared to complex chips, the PALCE16V8 is challenging to work with when attempting to recover, read out, or replicate its internal logic design. The difficulty stems from the encrypted fuse structures and the limited or blocked access interfaces, which are deliberately engineered to prevent copying or tampering.

We can extract PLD IC PALCE16V8, please view below chip features for your reference:

Features

· Active pull-up on data input pins

· Low power version (16V8L)

— 55 mA max. commercial (10, 15, 25 ns)

— 65 mA max. industrial (10, 15, 25 ns)

— 65 mA military (15 and 25 ns)

· Standard version has low power

— 90 mA max. commercial (10, 15, 25 ns)

— 115 mA max. commercial (7 ns)

— 130 mA max. military/industrial (10, 15, 25 ns)

· CMOS Flash technology for electrical erasability and reprogrammability

· PCI compliant

· User-programmable macrocell

— Output polarity control

— Individually selectable for registered or combinatorial operation

· Up to 16 input terms and 8 outputs

· 7.5 ns com’l version

5 ns tCO

5 ns tS

7.5 ns tPD

125-MHz state machine

· 10 ns military/industrial versions

7 ns tCO

10 ns tS

10 ns tPD

62-MHz state machine

· High reliability

— Proven Flash technology

— 100% programming and functional testing

Functional Description

The Cypress PALCE16V8 is a CMOS Flash Electrical Erasable second-generation programmable array logic device. It is implemented with the familiar sum-of-product (AND-OR) logic structure and the programmable macrocell.

Functional Description (continued)

The PALCE16V8 is executed in a 20-pin 300-mil molded DIP, a 300-mil cerdip, a 20-lead square ceramic leadless chip carrier, and a 20-lead square plastic leaded chip carrier. The device provides up to 16 inputs and 8 outputs. The PALCE16V8 can be electrically erased and reprogrammed. The programmable macrocell enables the device to function as a superset to the familiar 20-pin PLDs such as 16L8, 16R8, 16R6, and 16R4.

The PALCE16V8 features 8 product terms per output and 32 input terms into the AND array. The first product term in a macrocell can be used either as an internal output enable control or as a data product term. There are a total of 18 architecture bits in the PALCE16V8 macrocell; two are global bits that apply to all macrocells and 16 that apply locally, two bits per macrocell. The architecture bits determine whether the macrocell functions as a register or combinatorial with inverting or noninverting output.

The output enable control can come from an external pin or internally from a product term. The output can also be permanently enabled, functioning as a dedicated output or permanently disabled, functioning as a dedicated input. Feedback paths are selectable from either the input/output pin associated with the macrocell, the input/output pin associated with an adjacent pin, or from the macrocell register itself.

Configuration Table

All registers in the PALCE16V8 power-up to a logic LOW for predictable system initialization. For each register, the associated output pin will be HIGH due to active-LOW outputs.

Electronic Signature

An electronic signature word is provided in the PALCE16V8 that consists of 64 bits of programmable memory that can contain user-defined data.

Security Bit

A security bit is provided that defeats the readback of the internal programmed pattern when the bit is programmed.

Low Power

The Cypress PALCE16V8 provides low-power operation through the use of CMOS technology, and increased testability with Flash reprogrammability.

Product Term Disable

Product Term Disable (PTD) fuses are included for each product term. The PTD fuses allow each product term to be individually disabled.

Efforts to extract PLD IC PALCE16V8 content must navigate several technical hurdles:

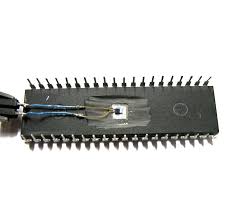

- Locked Fuse Configurations: Once the chip is in secure mode, direct readout of the fuse logic is prevented, requiring specialized reverse engineering techniques to decode the logic structure.

- No Standard Debug Ports: Unlike an MCU with JTAG or SPI interfaces, PLDs offer no standard ports for memory access, limiting typical tools from accessing internal data.

- Physical Protection: To further deter duplication, some units may be decapsulated and coated for protection, making physical probing and analysis more difficult and risky.

- No Firmware or Flash: Since there’s no traditional firmware or binary file, the recovery process focuses on logic gate configuration, making replication and duplication a highly technical task involving heximal structure interpretation.

Professional PLD Extraction and Replication Services

We specialize in secure and accurate extraction of programmable logic, including legacy and secured PLD chips such as the PALCE16V8. Our team combines in-depth knowledge of hardware design, proprietary tools, and non-destructive analysis methods to unlock and recover logic data without compromising the device’s functionality or integrity.

We offer the ability to clone, duplicate, and restore PALCE-based systems, even when original source code, logic files, or program archives are no longer available. Whether you’re trying to recover obsolete systems, replicate production logic for ongoing use, or migrate logic into newer platforms, our services ensure accuracy and legal compliance throughout the process.

Why Choose Our Service

- Specialized Experience in Legacy PLD Devices

- Advanced Equipment for Secure Extraction

- Ethical and Confidential Engagements

- Capability to Work with Encrypted and Locked Chips

If you need to extract PLD IC PALCE16V8, we provide the right solution with expert care. Let us help you open what others can’t and ensure your legacy systems continue to perform without compromise.

Tags: extract pld ic bin code,extract pld ic content,extract pld ic data,extract pld ic firmware,extract pld ic hex file,extract pld ic program