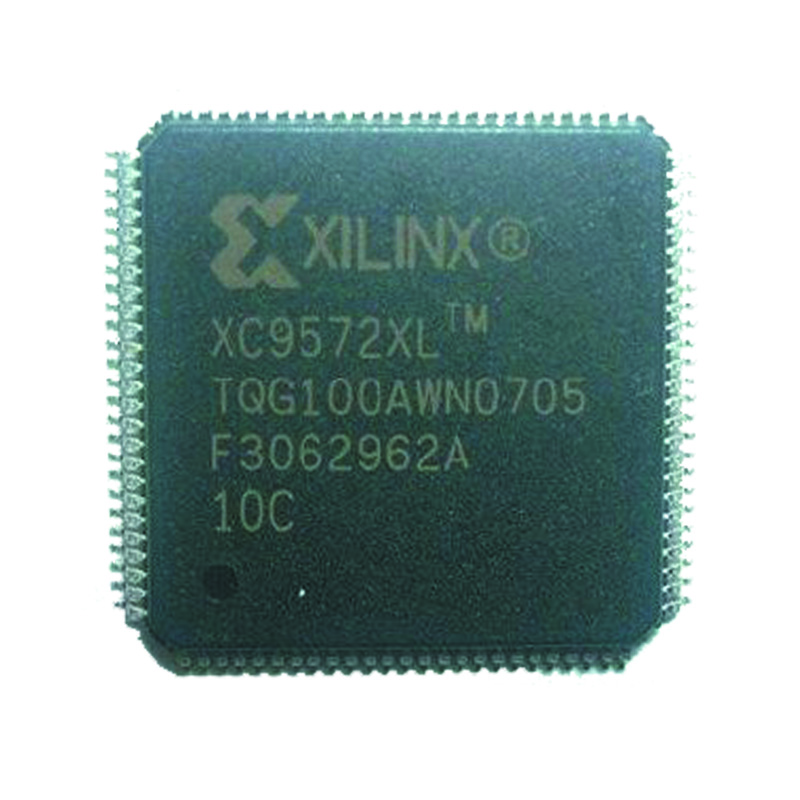

Decrypt CPLD IC Xilinx XC9572-15PQ100C

The Xilinx XC9572XL is a widely-used CPLD (Complex Programmable Logic Device) recognized for its reliability in industrial automation, communications, and embedded control systems. Unlike traditional MCUs or microprocessors, CPLDs like the XC9572XL are configured to execute logic operations with high speed and low latency. These chips store their program, typically written in VHDL or Verilog, in an internal flash-based memory array. When access to this configuration is lost or the device is locked, the need to decrypt CPLD IC Xilinx XC9572XL becomes essential for system restoration or duplication.

Understanding the Technology Behind XC9572XL

The XC9572XL offers 72 macrocells and supports in-system programming through JTAG, enabling flexible design updates even after deployment. To protect the integrity of proprietary logic designs, Xilinx provides secured configuration features, including readout protection, fuse bits, and encryption mechanisms. These security functions are designed to lock the embedded program and prevent unauthorized dumping, extraction, or reverse engineering of the device’s internal logic.

When a CPLD like the XC9572XL is secured, standard development tools cannot read out, replicate, or clone its contents. This presents a major obstacle for engineers or system integrators who need to recover, restore, or duplicate a legacy system when the original source code, binary file, or configuration archive is missing.

Challenges in Decrypting XC9572XL

Efforts to decrypt CPLD IC Xilinx XC9572XL face several difficulties:

- Fuse Bit Protection: Once the security fuse is blown, the chip enters a locked state, making it nearly impossible to open or access the program memory through conventional interfaces.

- Encrypted Configuration Data: The embedded configuration can be encrypted, requiring complex decode or decrypt processes to transform raw heximal or bitstream data into a usable logic design.

- No EEPROM Backup: Unlike MCUs with accessible EEPROM, CPLDs like the XC9572XL have no user-accessible non-volatile memory to retrieve data from after security is enabled.

- Physical Security: Devices are designed to resist decapsulation or physical probing, requiring advanced lab techniques to conduct low-level attacks or extractions.

Our Expert CPLD Decryption and Recovery Service

We offer specialized services to decrypt CPLD IC Xilinx XC9572XL, helping clients unlock, recover, and extract valuable configuration data from protected or secured CPLD devices. Whether you’ve lost the original configuration file, need to duplicate a system, or wish to restore production capability, we deliver professional, legally compliant solutions tailored to your needs.

Our services include:

- Non-destructive readout and recovery of locked CPLDs

- Reverse engineering and replication of lost designs

- Fuse bit analysis and potential removal for access recovery

- Full bitstream dump and binary file extraction from encrypted devices

Why Choose Us

- Deep expertise in Xilinx CPLD architecture and security features

- Access to industry-grade tools for secure readout, decoding, and replication

- Proven track record with encrypted, locked, and legacy programmable logic devices

- Confidential, legal, and results-driven approach

If you’re facing the challenge of a locked Xilinx XC9572XL, we provide the perfect end-to-end solution to extract, decrypt, and restore the embedded logic—securely and efficiently. Reach out to us to discuss your recovery or duplication project.

We can Decrypt CPLD IC Xilinx XC9572-15PQ100C, below chip features for your reference:

Features

7.5 ns pin-to-pin logic delays on all pins

fCNT to 125 MHz

72 macrocells with 1,600 usable gates

Up to 72 user I/O pins

5V in-system programmable

Product Specification

Description

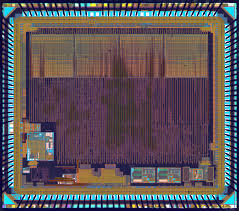

The XC9572 is a high-performance CPLD providing advanced in-system programming and test capabilities for general purpose logic integration. It is comprised of eight 36V18 Function Blocks, providing 1,600 usable gates with propagation delays of 7.5 ns. See Figure 2 for the architecture overview.

– Program/erase over full commercial voltage and temperature range

Enhanced pin-locking architecture to facilitate MCU reading

Flexible 36V18 Function Block

– 90 product terms drive any or all of 18 macrocells within Function Block

– Global and product term clocks, output enables, set and reset signals

Extensive IEEE Std 1149.1 boundary-scan (JTAG) support

Programmable power reduction mode in each macrocell

Slew rate control on individual outputs

User programmable ground pin capability by Reverse Engineering CPLD IC GAL16V8D

Extended pattern security features for design protection

High-drive 24 mA outputs

3.3V or 5V I/O capability

Advanced CMOS 5V FastFLASH™ technology

Supports parallel programming of more than one

XC9500 concurrently

Available in 44-pin PLCC, 84-pin PLCC, 100-pin PQFP, and 100-pin TQFP packages

Power Management

Power dissipation can be reduced in the XC9572 by configuring macrocells to standard or low-power modes of operation. Unused macrocells are turned off to minimize power dissipation.

Operating current for each design can be approximated for specific operating conditions using the following equation:

ICC (mA) = MCHP (1.7) + MCLP (0.9) + MC (0.006 mA/MHz) f

Where:

MCHP = Macrocells in high-performance mode

MCLP = Macrocells in low-power mode

MC = Total number of macrocells used f = Clock frequency (MHz)

Figure 1 shows a typical calculation for the XC9572 device.