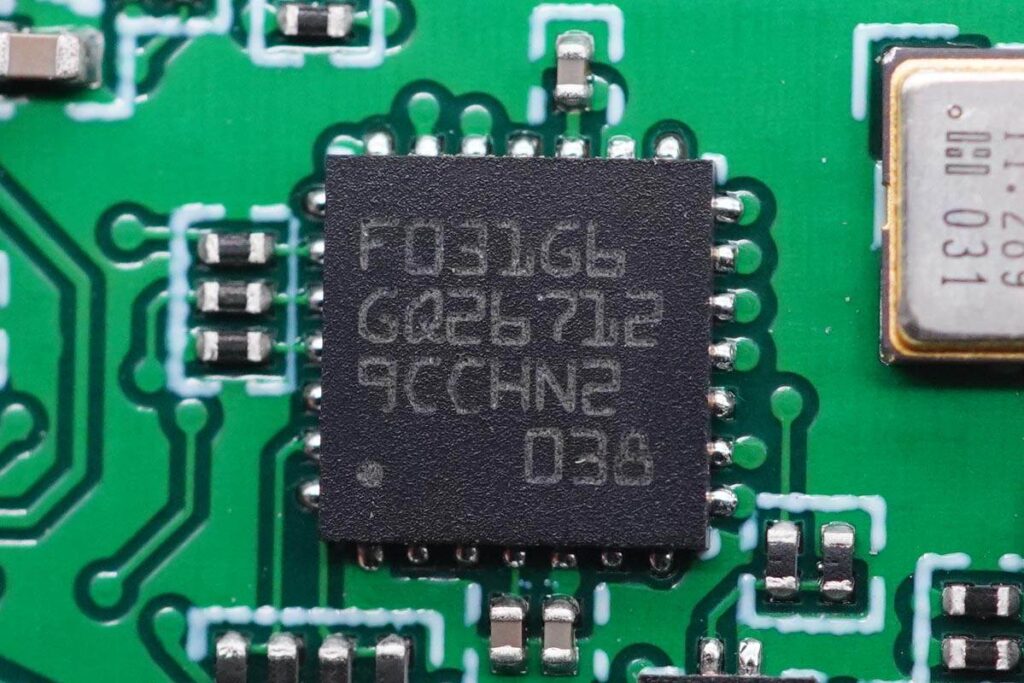

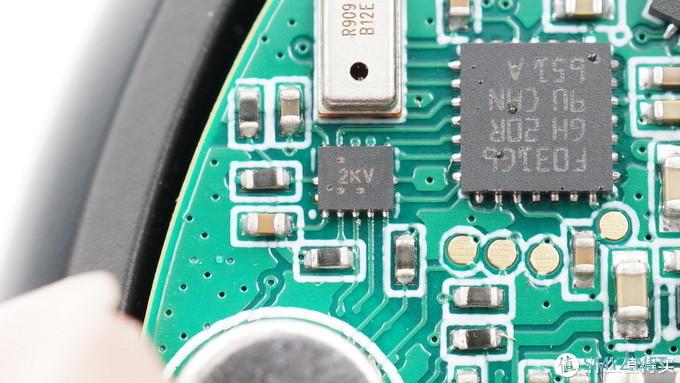

Cracking ARM STM32F031G6 Microprocessor Flash

Cracking ARM STM32F031G6 Microprocessor Flash locked bit and recover flash firmware from stm32f031g6 microcontroller memory, then unlocked stm32f031g6 microprocessor flash memory content will be readout;

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure.

If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator) to decode stm32f031k4 microcontroller’s flash firmware.

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions by cracking stm32f031g4 microprocessor’s locked bit. The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.