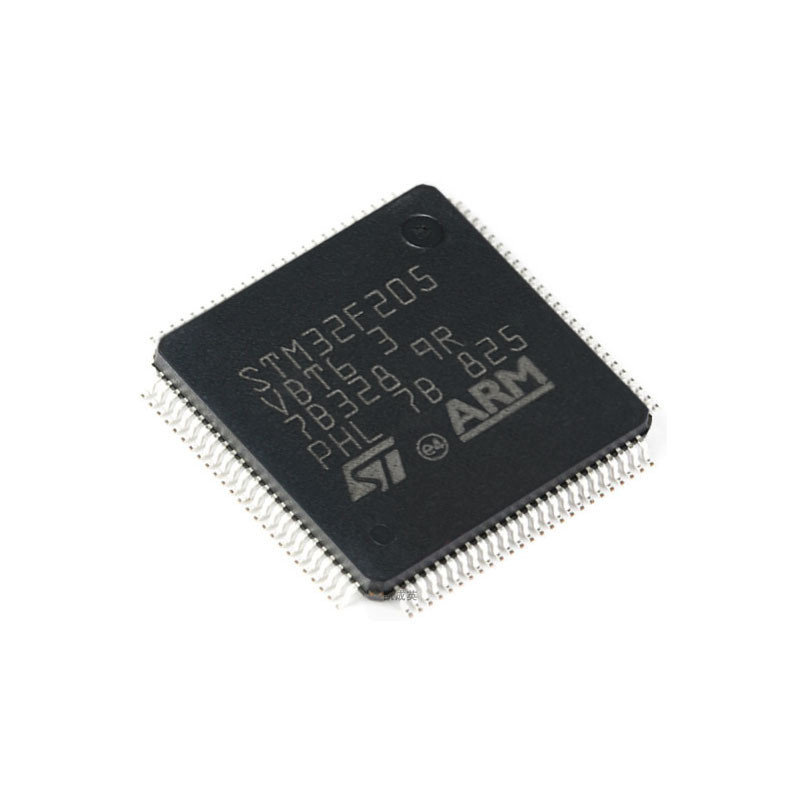

Crack Protective STM32F205VC MCU Flash Memory

Crack Protective STM32F205VC MCU Flash Memory and recover embedded heximal file from stm32f205vc microprocessor flash memory, decode arm microcontroller secured memory program software;

The following conditions must be respected:

- VDD must always be higher than VCAP_1 and VCAP_2 to avoid current injection between power domains.

- If the time for VCAP_1 and VCAP_2 to reach 1.08 V is faster than the time for VDD to reach 1.8 V, then PA0 must be kept low to cover both conditions: until VCAP_1 and VCAP_2 reach 1.08 V and until VDD reaches 1.8 V (see Figure 8) when crack arm mcu stm32f205rb protective system.

- Otherwise, If the time for VCAP_1 and VCAP_2 to reach 1.08 V is slower than the time for VDD to reach 1.8 V, then PA0 must be asserted low externally (see Figure 9).

- If VCAP_1 and VCAP_2 go below 1.08 V and VDD is higher than 1.8 V, then a reset must be asserted on PA0 pin.

Regulator OFF / internal reset OFF

On WLCSP64+2 package, this mode activated by connecting REGOFF to VSS and IRROFF to VDD. IRROFF cannot be activated in conjunction with REGOFF. This mode is available only on the WLCSP64+2 package. It allows to supply externally a 1.2 V voltage source through VCAP_1 and VCAP_2 pins to unlock stm32f205rc secured microcontroller flash program. In this mode, the integrated power-on reset (POR)/ power- down reset (PDR) circuitry is disabled.

An external power supply supervisor must monitor both the external 1.2 V and the external VDD supply voltage, and must maintain the device in reset mode as long as they remain below a specified threshold. The VDD specified threshold, below which the device must be maintained under reset, is 1.8 V. This supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.