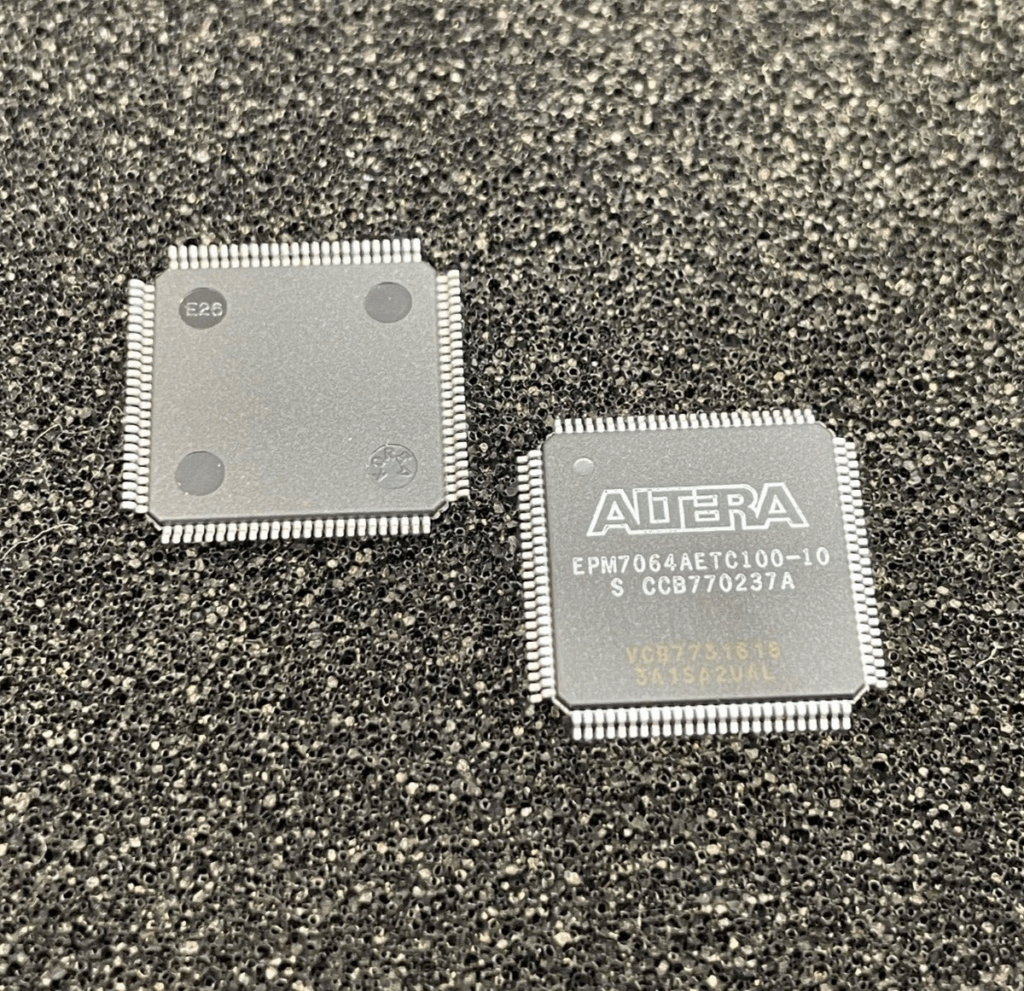

Crack PLD IC Altera EPM7064AETC100-4N

Crack PLD IC Altera EPM7064AETC100-4N is a phrase often used to describe legitimate efforts—by product owners, OEMs, and authorized service providers—to regain access to programmable logic device (PLD) configuration data when the original design files are lost, corrupted, or the device becomes inaccessible. The Altera EPM7064AETC family (CPLD/JTAG-era devices) stores design configuration in a proprietary file format (commonly a JED file or similar), and that configuration is the intellectual property that defines the device’s behavior in hardware systems.

Crack PLD IC Altera EPM7064AETC100-4N jed file, needs to disable its memory program protection system and readout the jed file from it:

– MAX 7000AE device in-system programmability (ISP) circuitry compliant with IEEE Std. 1532

– EPM7128A and EPM7256A device ISP circuitry compatible with IEEE Std. 1532

Built-in boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1

Supports JEDEC Jam Standard Test and Programming Language (STAPL) JESD-71

Enhanced ISP features

– Enhanced ISP algorithm for faster programming (excluding EPM7128A and EPM7256A devices)

– ISP_Done bit to ensure complete programming (excluding EPM7128A and EPM7256A devices)

– Pull-up resistor on I/O pins during in-system

— Pin-compatible with the popular 4.5-ns pin-to-pin logic delays with counter frequencies of up to 227.3 MHz

Supports hot-socketing in MAX 7000AE devices

Programmable interconnect array (PIA) continuous routing structure for fast, predictable performance

PCI-compatible

Bus-friendly architecture, including programmable slew-rate control

Open-drain output option

Programmable macrocell registers with individual clear, preset, clock, and clock enable controls

Programmable power-up states for macrocell registers in MAX 7000AE devices

Programmable power-saving mode for 50% or greater power reduction in each macrocell

Configurable expander product-term distribution, allowing up to 32 product terms per macrocell

Programmable security bit for protection of proprietary designs 6 to 10 pin- or logic-driven output enable signals

Two global clock signals with optional inversion

Enhanced interconnect resources for improved routability

Fast input setup times provided by a dedicated path from I/O pin to macrocell registers

Programmable output slew-rate control from Crack PLD IC Altera EPM7064AETC100-4N

Why Organizations Need Recovery or Duplication

In many industries the configuration stored on CPLDs and PLDs is critical:

- Industrial control systems rely on PLDs for glue-logic, timing, and safety interlocks.

- Telecommunications and networking use PLDs for protocol bridging and custom interfaces.

- Medical devices and instrumentation sometimes depend on CPLD timing and deterministic logic.

- Aerospace and defense platforms use hardened programmable logic for reliable hardware functions.

When original source (HDL) or the programmed JED/archive is lost, legitimate owners may require extraction, replication, or duplication of the configuration to support maintenance, produce replacement boards, or migrate to modern FPGA solutions.

Technical Complexities and Non-Actionable Challenges

Extracting and restoring configuration from a secured PLD involves significant, non-trivial challenges that go beyond “press a button” solutions:

- Protection Mechanisms: Vendors implement protection to prevent unauthorized copying or tampering; these controls are intentional safeguards for IP and product safety.

- Proprietary Formats: Configuration archives and device fuses may be stored in vendor-specific binary or JED-like formats that require careful interpretation.

- Physical Risk: Invasive analysis or careless handling can damage the device or erase configuration, risking permanent data loss.

- Reconstruction Difficulty: Even when a partial dump is available, reconstructing a fully functioning HDL or functional equivalent can require substantial reverse engineering and validation work.

- Compliance & Ownership: Legal restrictions and IP ownership must be clearly established before any recovery work begins.

Programmable ground pins

Software design support and automatic place-and-route provided by Altera’s development systems for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and VeriBest. Programming support with Altera’s Master Programming Unit (MPU), MasterBlasterTM serial/universal serial bus (USB) communications cable, ByteBlasterMVTM parallel port download cable, and BitBlasterTM serial download cable, as well as programming hardware from third-party manufacturers and any JamTM STAPL File (.jam), Jam Byte-Code File (.jbc), or Serial Vector Format File (.svf) capable in-circuit tester.

Legitimate Purposes & Responsible Services

Legitimate reasons for seeking recovery include disaster recovery, product lifecycle support, migration to newer hardware, and forensic analysis after a failure. Responsible service providers focus on legal compliance, traceable authorization, and data preservation rather than exploitation. Typical, lawful offerings include: secure diagnostics, non-destructive forensic capture, data preservation and archival, authorized replication for replacement boards, and migration planning to modern FPGAs or SOCs.

Why Choose a Professional Partner

A qualified service provider brings: deep familiarity with PLD ecosystems, strict confidentiality and chain-of-custody procedures, non-destructive handling practices, and legal/ethical safeguards to ensure any work is performed only with documented authorization. This minimizes risk to the device, protects IP, and restores operational continuity for the client.

Summary

When an organization needs to extract, recover, or duplicate configuration from a PLD such as the Altera EPM7064AETC100-4N, success depends on specialist expertise, lawful authorization, and careful, non-destructive processes. If you are the device owner or have explicit authorization to perform recovery or migration, contact a reputable, legally compliant service provider for a confidential consultation and an approved recovery plan.