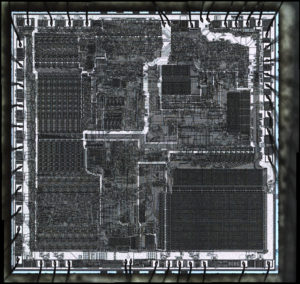

Crack Microprocessor ATMEGA164A Hex

Crack Microprocessor ATMEGA164A flash and eeprom memory, then extract IC firmware out from them in the format of Heximal or binary, and then copy file to blank MCU ATmega164A;

Crack Microprocessor ATMEGA164A flash and eeprom memory, then extract IC firmware out from them in the format of Heximal or binary, and then copy file to blank MCU ATmega164A

Due to the high-speed operation of the XRAM interface, the address latch must be selected with care for system frequencies above 8 MHz @ 4V and 4 MHz @ 2.7V.

When operating at conditions above these frequencies, the typical old style 74HC series latch becomes inadequate. The External Memory Interface is designed in compliance to the 74AHC series latch. However, most latches can be used as long they comply with the main timing parameters if unlock microprocessor pic18f4420 flash memory.

The main parameters for the address latch are:

D to Q propagation delay (tPD).

Data setup time before G low (tSU).

Data (address) hold time after G low (TH)

The External Memory Interface is designed to guaranty minimum address hold time after G is asserted low of th = 5 ns. Refer to tLAXX_LD/tLLAXX_ST in “External Data Memory Timing” Tables 169 through Tables 176 on pages 376 – 378. The D-to-Q propagation delay (tPD) must be taken into consideration when calculating the access time requirement of the external component. The data setup time before G low (tSU) must not exceed address valid to ALE low (tAVLLC) minus PCB wiring delay (dependent on the capacitive load).

The pull-ups on the AD7:0 ports may be activated if the corresponding Port register is written to one. To reduce power consumption in sleep mode, it is recommended to disable the pull-ups by writing the Port register to zero before entering sleep.

The XMEM interface also provides a bus-keeper on the AD7:0 lines. The bus-keeper can be disabled and enabled in software as described in “External Memory Control Register B – XMCRB” on page 35. When enabled, the bus-keeper will keep the previous value on the AD7:0 bus while these lines are tri-stated by the XMEM interface after read mcu pic18f2510 program.

External Memory devices have different timing requirements. To meet these requirements, the XMEM interface provides four different wait-states as shown in Table 5. It is important to consider the timing specification of the External Memory device before selecting the wait-state.

The most important parameters are the access time for the external memory compared to the set-up requirement. The access time for the External Memory is defined to be the time from receiving the chip select/address until the data of this address actually is driven on the bus.

The access time cannot exceed the time from the ALE pulse must be asserted low until data is stable during a read sequence (See tLLRL+ tRLRH – tDVRH in Tables 169 through Tables 176 on pages 376 – 378). The different wait-states are set up in software. As an additional feature, it is possible to divide the external memory space in two sectors with individual wait-state settings before read chip pic18f2610 firmware.

This makes it possible to connect two different memory devices with different timing requirements to the same XMEM interface. For XMEM interface timing details, please refer to Table 169 to Table 176 and Figure 161 to Figure 164 in the “External Data Memory Timing” on page 376.

Tags: crack microprocessor archive,crack microprocessor bin,crack microprocessor code,crack microprocessor content,crack microprocessor data,crack microprocessor eeprom,crack microprocessor file,crack microprocessor firmware,crack microprocessor hex,crack microprocessor information,crack microprocessor memory,crack microprocessor program