Crack MCU ST7FLITEBCM6 Locked Eeprom Memory

Through reasonable interrupt on the instructions will greatly help engineer to Crack MCU ST7FLITEBCM6 Locked Eeprom Memory, below we will try to introduce some of the operational mechanism and fundamental constitution for you:

The ST7 enhanced interrupt management pro- vides the following features:

Hardware interrupts

Software interrupt (TRAP)

Nested or concurrent interrupt management with flexible interrupt priority and level management:

– Up to 4 software programmable nesting levels

– Up to 16 interrupt vectors fixed by hardware

– 2 non maskable events: RESET, TRAP

– 1 maskable top level event: MCES This interrupt management is based on:

– Bit 5 and bit 3 of the CPU CC register (I1:0),

– Interrupt software priority registers (ISPRx),

– Fixed interrupt vector addresses located at the high addresses of the memory map (FFE0h to FFFFh) sorted by hardware priority order by recover MCU.

This enhanced interrupt controller guarantees full upward compatibility with the standard (not nest- ed) ST7 interrupt controller.

Crack MCU ST7FLITEBCM6 Locked Eeprom Memory

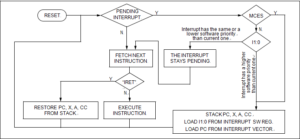

Regarding the 7.2 MASKING AND PROCESSING FLOW, The interrupt masking is managed by the I1 and I0 bits of the CC register and the ISPRx registers which give the interrupt software priority level of each interrupt vector (see Table 6). The processing flow is shown in below Figure

When an interrupt request has to be serviced:

– Normal processing is suspended at the end of the current instruction execution.

– The PC, X, A and CC registers are saved onto the stack.

– I1 and I0 bits of CC register are set according to the corresponding values in the ISPRx registers of the serviced interrupt vector.

– The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to “Interrupt Mapping” table for vector addresses).

The interrupt service routine should end with the IRET instruction which causes the contents of the saved registers to be recovered from the stack and Microcontroller ST7FLITE39F2M6 Heximal Unlocking will be completely smoothly.

Note: As a consequence of the IRET instruction, the I1 and I0 bits will be restored from the stack and the program in the previous level will resume.