Crack Freescale SPC5604EEF2MLH Microprocessor Flash Memory

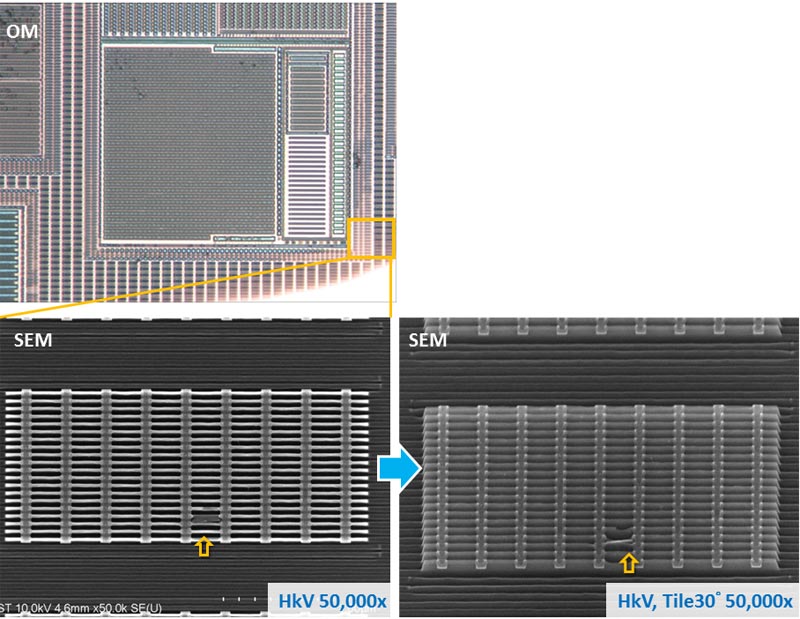

Crack Freescale SPC5604EEF2MLH Microprocessor Flash Memory will disable its memory protection unit and then readout embedded heximal file from MCU’s flash memory directly through universal programmer, the original firmware inside micrprocessor will be recovered;

The main oscillator provides these features:

Input frequency range: 4–40 MHz

Crystal input mode or oscillator input mode

PLL reference

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor which can be used for reading nxp microprocessor spc5602df1m1 flash memory program. The voltage at the capacitor is compared by the stable bandgap reference voltage.

The RC oscillator provides these features:

- Nominal frequency 16 MHz

- ±5% variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the PLL

- RC oscillator is used as the default system clock during startup

The PIT module implements these features:

- 4 general-purpose interrupt timers

- 32-bit counter resolution

- Clocked by system clock frequency

- Each channel usable as trigger for a DMA request

The STM implements these features:

- One 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode