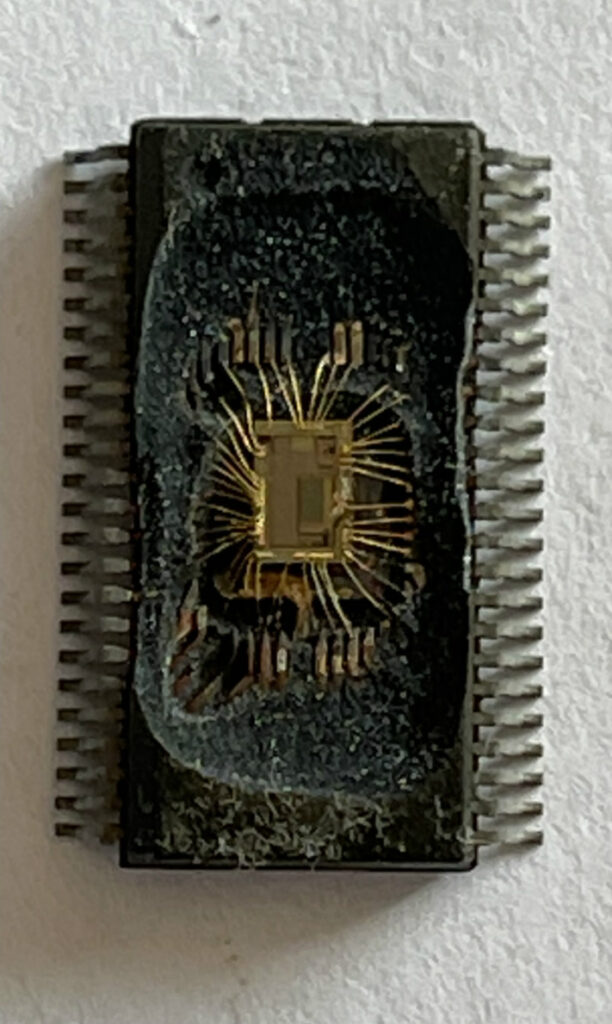

Crack Freescale SPC5603BAMLL4R Microcontroller Locked Bit

Crack Freescale SPC5603BAMLL4R Microcontroller Locked Bit and readout embedded firmware content from spc5603bam mcu flash memory, and copy flash data to new microprocessor;

The device implements a power-on reset (POR) module to ensure correct power-up initialization, as well as five low voltage detectors (LVDs) to monitor the VDD and the VDD_LV voltage while device is supplied:

POR monitors VDD during the power-up phase to ensure device is maintained in a safe reset state (refer to RGM Destructive Event Status (RGM_DES) Register flag F_POR in device reference manual)

LVDHV3 monitors VDD to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM_DES) Register flag F_LVD27 in device reference manual) when extract spc5602df1 microcontroller flash data.

LVDHV3B monitors VDD_BV to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM_DES) Register flag F_LVD27_VREG in device reference manual)

LVDHV5 monitors VDD when application uses device in the 5.0 V ± 10% range (refer to RGM Functional Event Status (RGM_FES) Register flag F_LVD45 in device reference manual)

LVDLVCOR monitors power domain No. 1 (refer to RGM Destructive Event Status (RGM_DES) Register flag F_LVD12_PD1 in device reference manual)

LVDLVBKP monitors power domain No. 0 (refer to RGM Destructive Event Status (RGM_DES) Register flag F_LVD12_PD0 in device reference manual) in the process of reading spc5602df1m microprocessor flash program code;