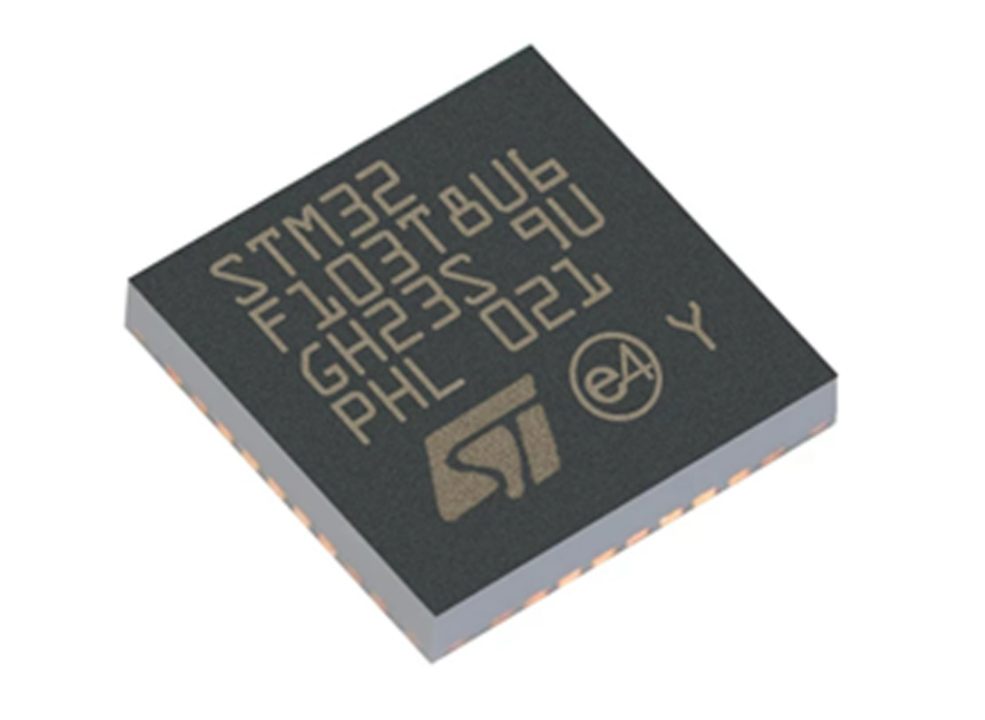

Crack ARM Microprocessor STM32F103T8

Crack ARM Microprocessor STM32F103T8 and restoring secured microcontroller stm32f103t8 flash program code from its memory, copy memory firmware to new microcomputer stm32f103t8;

64 or 128 Kbytes of embedded Flash is available for storing programs and data.

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial. Among other applications, CRC-based techniques are used to verify data transmission or storage integrity to pull out stm32f103t8 microcontroller flash data. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link- time and stored at a given memory location.

Twenty Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

The STM32F103xx performance line embeds a nested vectored interrupt controller able to handle up to 43 maskable interrupt channels (not including the 16 interrupt lines of Cortex®- M3) and 16 priority levels. This hardware block provides flexible interrupt management features with minimal interrupt latency.

The external interrupt/event controller consists of 19 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently after cracking stm32f103ve ic mcu flash memory. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 80 GPIOs can be connected to the 16 external interrupt lines.