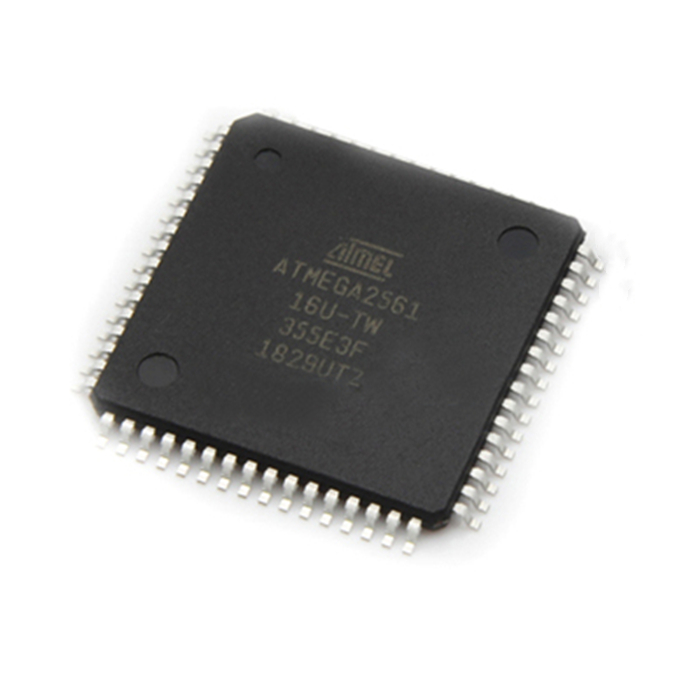

Break Microchip ATmega2561V MCU Flash Memory

Break Microchip ATmega2561V MCU Flash Memory is a process to attack atmega2561v microcontroller protective system and then copy embedded firmware to new microprocessor atmega2561v;

The Bit Copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source or destination for the oper- ated bit. A bit from a register in the Register File can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the Register File by the BLD instruction.

The Half Carry Flag H indicates a Half Carry in some arithmetic operations. Half Carry Is useful in BCD arithmetic. See the “Instruction Set Summary” on page 404 for detailed information.

The Register File is optimized for the AVR Enhanced RISC instruction set. In order to achieve the required performance and flexibility to unlock atmega2561v mcu flash memory binary file, the following input/output schemes are supported by the Register File:

- One 8-bit output operand and one 8-bit result input

- Two 8-bit output operands and one 8-bit result input

Two 8-bit output operands and one 16-bit result input

One 16-bit output operand and one 16-bit result input

Most of the instructions operating on the Register File have direct access to all registers, and most of them are sin- gle cycle instructions.

As shown in Figure 7-2, each register is also assigned a data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations to crack atmega2561v chip memory heximal content, this memory organization provides great flexibility in access of the registers, as the X-, Y- and Z-pointer registers can be set to index any register in the file.