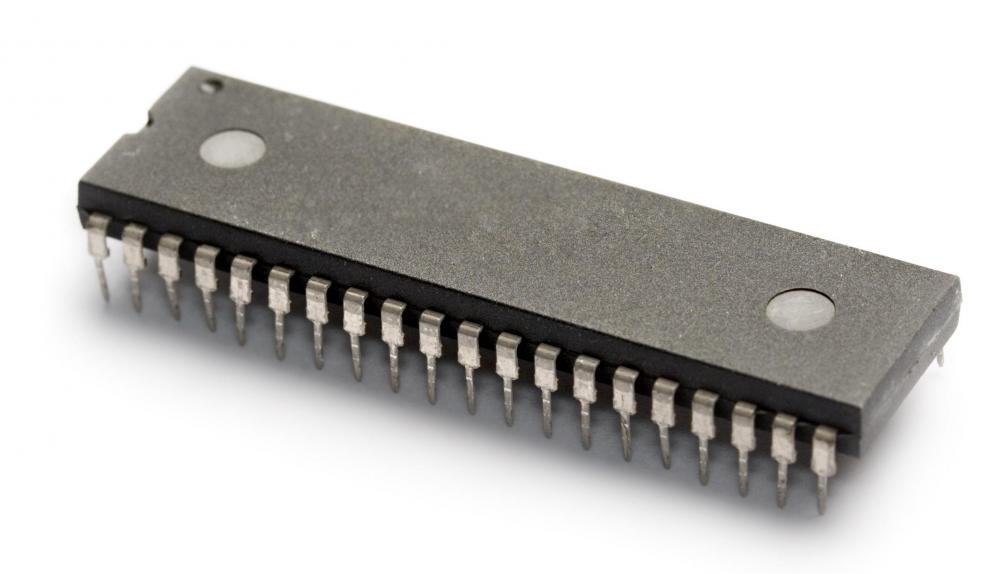

Break ATMEL ATMEGA640V Secured Microcontroller Fuse bit

Break ATMEL ATMEGA640V Secured Microcontroller Fuse bit is a process to recover embedded firmware from atmega640v microprocessor’s flash memory, read heximal content out from atmega640v mcu;

The ATmega640V is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful ins t ructions in a single clock cycle, the ATmega640v achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR® core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle when cracking atmega640v mcu heximal file. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega640v provides the following features: 64K/128K/256K bytes of In-System Programmable Flash with Read-While-Write capabilities, 4Kbytes EEPROM, 8Kbytes SRAM, 54/86 general purpose I/O lines, 32 general purpose working registers, Real Time Counter (RTC), six flexible Timer/Counters with compare modes and PWM, four USARTs by unlocking atmega640v mcu program from flash memory, a byte oriented 2-wire Serial Interface, a 16-channel, 10-bit ADC with optional differential input stage with programmable gain, programmable Watchdog Timer with Internal Oscillator, an SPI serial port, IEEE® std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming and six software selectable power saving modes.