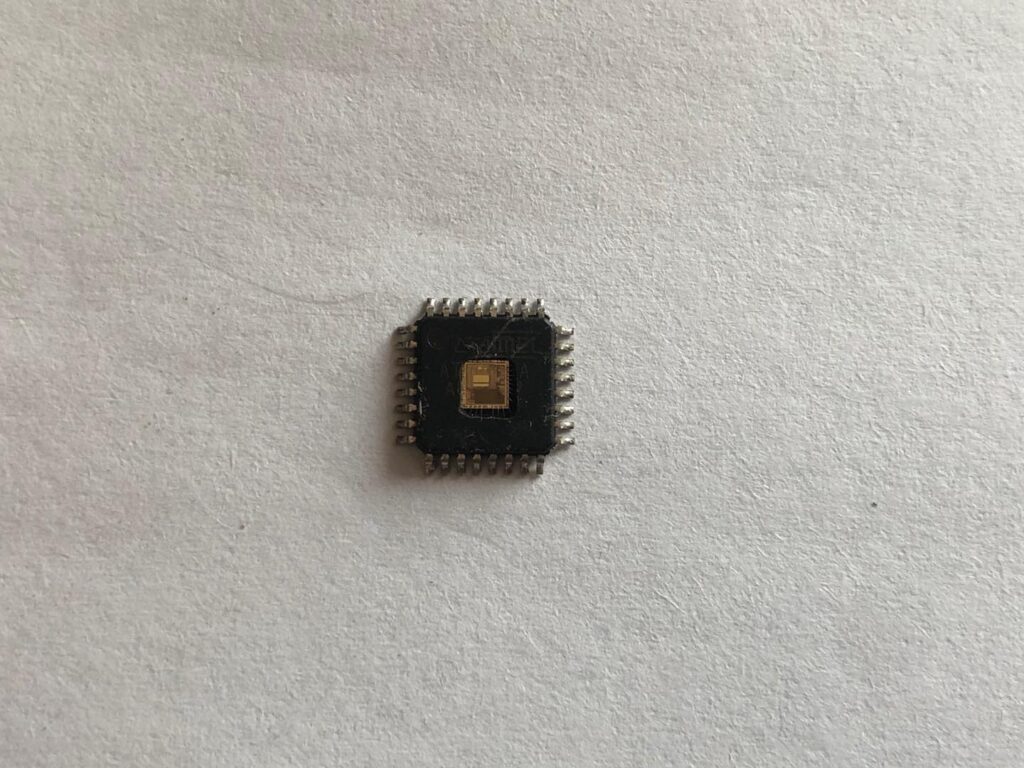

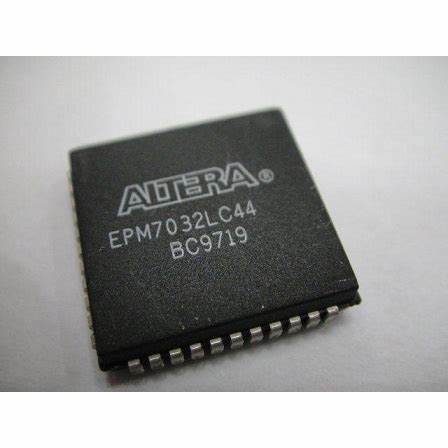

Altera EPM7032LC44 CPLD Eeprom POF Replication

Altera EPM7032LC44 CPLD Eeprom POF Replication starts from the process of reverse epm7032lc44 chip protective system, and then extract embedded data from epm7032lc44 EE PLD chip memory;

MAX 7000A devices offer a power-saving mode that supports low-power operation across user-defined signal paths or the entire device.

This feature allows total power dissipation to be reduced by 50% or more because most logic applications require only a small fraction of all gates to operate at maximum frequency by retrieve epm7064stc44 cpld memory code.

The designer can program each individual macrocell in a MAX 7000A device for either high-speed (i.e., with the Turbo BitTM option turned on) or low-power operation (i.e., with the Turbo Bit option turned off).

As a result, speed-critical paths in the design can run at high speed, while the remaining paths can operate at reduced power and breaking epm7064lc68 altera cpld protection. Macrocells that run at low power incur a nominal timing delay adder (tLPA) for the tLAD, tLAC, tIC, tEN, tSEXP, tACL, and tCPPW parameters.