Unlock Microcontroller ATTINY261A Flash

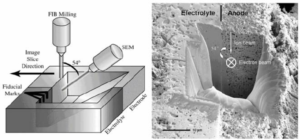

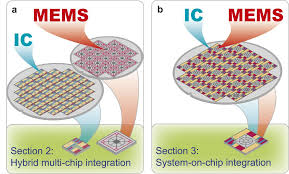

Unlock Microcontroller ATTINY261A Flash memory and extract IC code from the eeprom and flash memory, after cutting of the security fuse bit inside the MCU, the embedded firmware can be fully dump into the computer in the format of binary or heximal;

Unlock Microcontroller ATTINY261A Flash memory and extract IC code from the eeprom and flash memory, after cutting of the security fuse bit inside the MCU, the embedded firmware can be fully dump into the computer in the format of binary or heximal

The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with Pre-decrement, and Indirect with Post-increment.

In the Register file, registers R26 to R31 feature the indirect addressing pointer registers. The direct addressing reaches the entire data space. The Indirect with Displacement mode reaches 63 address locations from the base address given by the Y- or Z-register.

When using register indirect addressing modes with automatic pre-decrement and post increment, the address registers X, Y, and Z are decremented or incremented before read chip pic16f877 program.

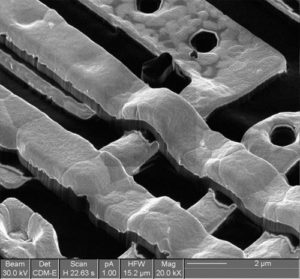

The 32 general purpose working registers, 64 I/O registers, and the 4,196/8,192 bytes of internal data SRAM in the ATtiny261a are all accessible through all these addressing modes.

This section describes the general access timing concepts for internal memory access. The internal data SRAM access is performed in two clk CPU cycles as described in Figure 13.

The ATtiny261a contains 4K bytes of data EEPROM memory. Itis organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described in the following, specifying the EEPROM Address Registers, the EEPROM Data Register, and the EEPROM Control Register if crack mcu pic12c672 hex.

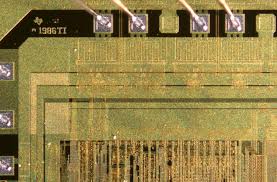

For a detailed description of SPI, JTAG and Parallel data downloading to the EEPROM, The EEPROM Access Registers are accessible in the I/O space. The write access time for the EEPROM is given in Table 3. A self-timing function, however, lets the user software detect when the next byte can be written. If the user code contains instructions that write the EEPROM, some precautions must be taken.

In heavily filtered power supplies, VCC is likely to rise or fall slowly on power-up/down. This causes the device for some period of time to run at a voltage lower than specified as minimum for the clock frequency used. for details on how to avoid problems in these situations.

In order to prevent unintentional EEPROM writes, a specific write procedure must be followed. Refer to the description of the EEPROM Control Register for details on this. When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed. When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed.

Tags: unlock microcontroller archive,unlock microcontroller bin,unlock microcontroller code,unlock microcontroller content,unlock microcontroller data,unlock microcontroller eeprom,unlock microcontroller file,unlock microcontroller firmware,unlock microcontroller hex,unlock microcontroller information,unlock microcontroller memory,unlock microcontroller program