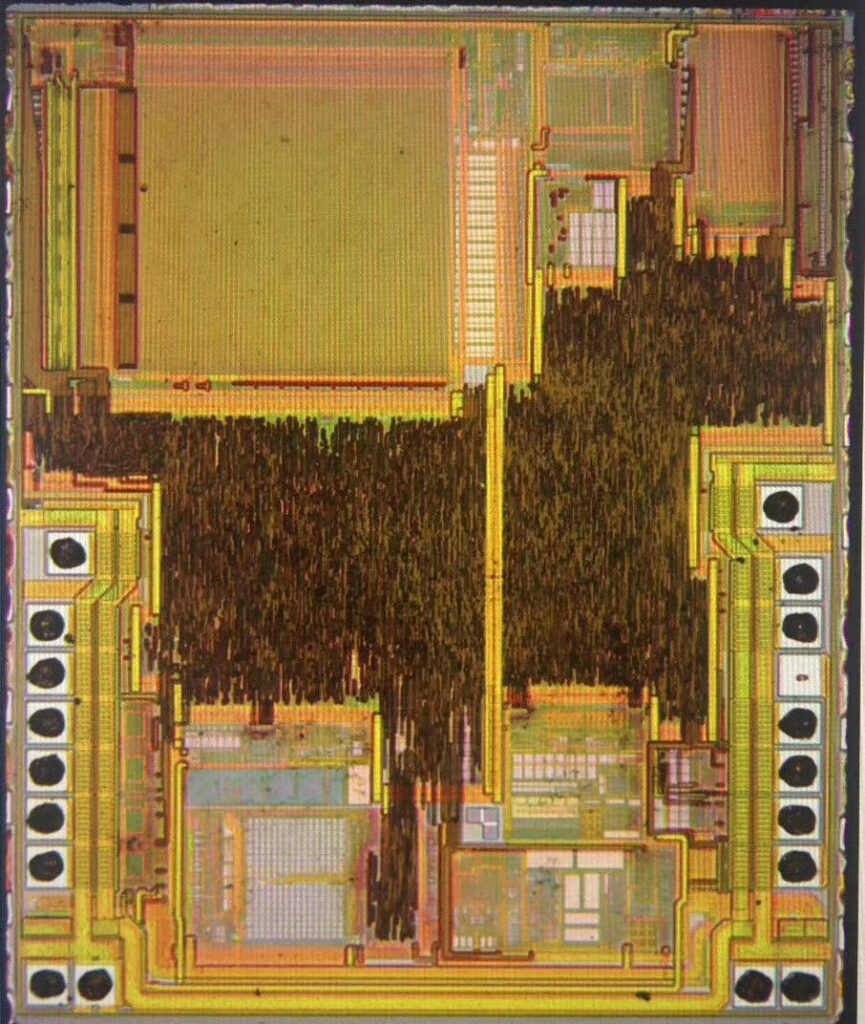

Unlock Microcontroller ATMEGA64A Firmware

Unlock Microcontroller ATMEGA64A through the developed MCU reading technique, the program of flash memory and data from eeprom memory can be fully readout from the ATmega64A then reprogramme the firmware to other blank MCU;

Unlock Microcontroller ATMEGA64A through the developed MCU Cracking technique, the program of flash memory and data from eeprom memory can be fully readout from the ATmega64A then reprogramme the firmware to other blank MCU

The USART Transmitter has two flags that indicate its state: USART Data Register Empty (UDREn) and Transmit Complete (TXCn). Both flags can be used for generating interrupts.

The Data Register Empty (UDREn) Flag indicates whether the transmit buffer is ready to receive new data. This bit is set when the transmit buffer is empty, and cleared when the transmit buffer contains data to be transmitted that has not yet been moved into the Shift Register if clone atmel at89s8252 Microcontroller.

For compatibility with future devices, always write this bit to zero when writing the UCSRnA Register. When the Data Register Empty Interrupt Enable (UDRIEn) bit in UCSRnB is written to one.

The USART Data Register Empty Interrupt will be executed as long as UDREn is set (provided that global interrupts are enabled). UDREn is cleared by writing UDRn.

When interrupt-driven data transmission is used, the Data Register Empty interrupt routine must either write new data to UDRn in order to clear UDREn or disable the Data Register Empty interrupt, otherwise a new interrupt will occur once the interrupt routine terminates.

The Transmit Complete (TXCn) Flag bit is set one when the entire frame in the Transmit Shift Register has been shifted out and there are no new data currently present in the transmit buffer.

The TXCn Flag bit is automatically cleared when a transmit complete interrupt is executed, or it can be cleared by writing a one to its bit location.

The TXCn Flag is useful in half-duplex communication interfaces (like the RS-485 standard), where a transmitting application must enter receive mode and free the communication bus immediately after completing the transmission.

When the Transmit Compete Interrupt Enable (TXCIEn) bit in UCSRnB is set, the USART Transmit Complete Interrupt will be executed when the TXCn Flag becomes set (provided that global interrupts are enabled).

When the transmit complete interrupt is used, the interrupt handling routine does not have to clear the TXCn Flag, this is done automatically when the interrupt is executed.

Tags: unlock microcontroller heximal archive,unlock microcontroller heximal code,unlock microcontroller heximal content,unlock microcontroller heximal data,unlock microcontroller heximal eeprom,unlock microcontroller heximal file,unlock microcontroller heximal firmware,unlock microcontroller heximal information,unlock microcontroller heximal memory,unlock microcontroller heximal program