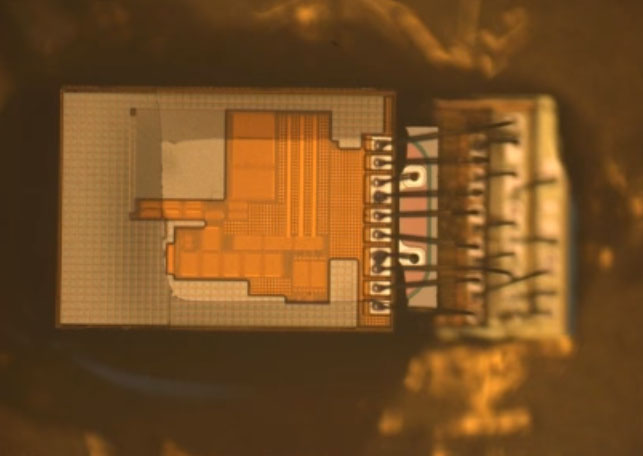

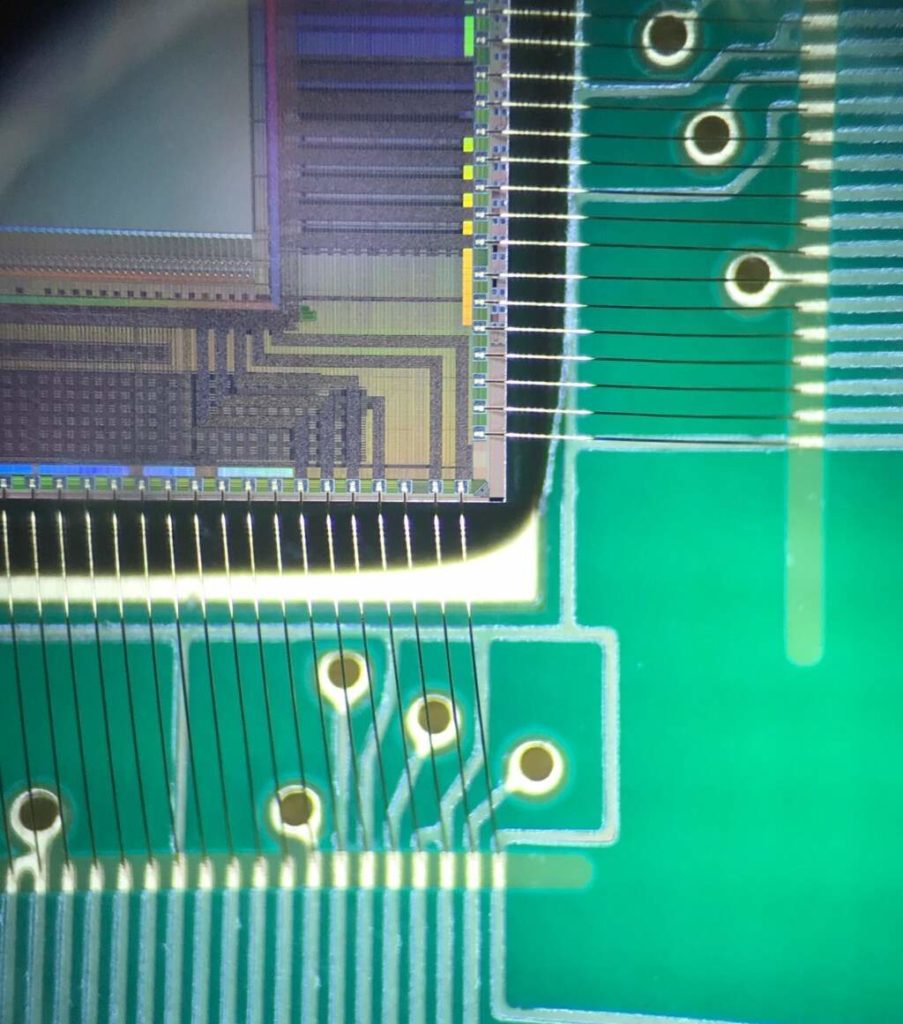

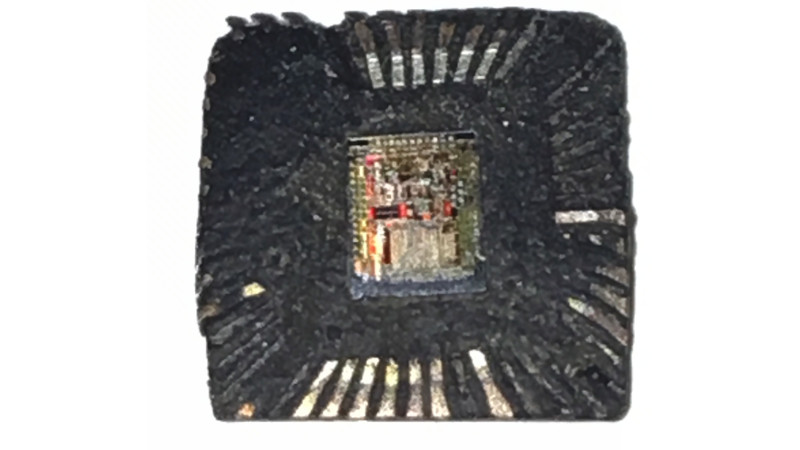

Unlock Microcontroller AT89C51IC2 Program

Unlock Microcontroller AT89C51IC2 and extract IC Program from flash and eeprom memory, recover embedded firmware in the format of heximal from mcu at89c51ic2;

The CMOD register includes three additional bits associated with the PCA (See Figure 11 and Table 26).

The CIDL bit which allows the PCA to stop during idle mode.

The WDTE bit which enables or disables the watchdog function on module 4. The ECF bit which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows when crack microchip pic16f57 microcontroller.

The CCON register contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (Refer to Table 27).

Bit CR (CCON.6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

Bit CF: The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software.

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. (See Table 28). The registers contain the bits that control the mode that each module will operate in.

The ECCF bit (CCAPMn.0 where n=0, 1, 2, 3, or 4 depending on the module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module.

PWM (CCAPMn.1) enables the pulse width modulation mode. The TOG bit (CCAPMn.2) when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module’s capture/compare register after attack cpld altera epm7128elc84.

The match bit MAT (CCAPMn.3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the module’s capture/compare register.

The next two bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition.

The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function.

To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module’s capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated.

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module’s capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (See Figure 14).

Tags: unlock microcontroller embedded archive,unlock microcontroller embedded code,unlock microcontroller embedded content,unlock microcontroller embedded data,unlock microcontroller embedded eeprom,unlock microcontroller embedded file,unlock microcontroller embedded firmware,unlock microcontroller embedded information,unlock microcontroller embedded memory,unlock microcontroller embedded program