Recover Microchip MCU PIC16F628A Binary

Recover Microchip MCU PIC16F628A Binary from Microcontroller PIC16F628A flash memory, copy the firmware into blank MCU PIC16F628A which will provide the same functions as original microprocessor which has been reverse engineering;

Recover Microchip MCU PIC16F628A Binary from Microcontroller PIC16F628A flash memory, copy the firmware into blank MCU PIC16F628A which will provide the same functions as original version

GENERAL DESCRIPTION

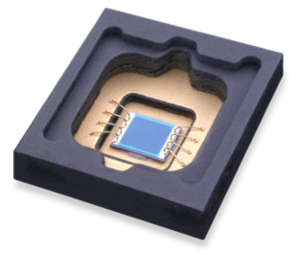

The PIC16F628A are 18-Pin FLASH based members of the versatile PIC16CXX family of low cost, high performance, CMOS, fully-static, 8-bit microcontrollers

All PICmicro® microcontrollers employ an advanced RISC architecture. The PIC16F628A have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available, complemented by a large register set.

PIC16F628A microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC16F628A devices have integrated features

The PIC16F628A has 8 oscillator configurations. The single-pin RC oscillator provides a low cost solution. The LP oscillator minimizes power consumption, XT is a standard crystal, and INTOSC is a self contained precision two-speed internal oscillator.

RISC architecture. The PIC16F628A have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single- cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available, complemented by a large register set

PIC16F627A/628A/648A microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

Tags: recover microchip mcu binary archive,recover microchip mcu binary code,recover microchip mcu binary content,recover microchip mcu binary data,recover microchip mcu binary eeprom,recover microchip mcu binary file,recover microchip mcu binary firmware,recover microchip mcu binary information,recover microchip mcu binary memory,recover microchip mcu binary program