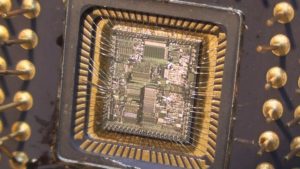

Read Microcontroller STMicroelectronics ST19NA18

Read Microcontroller STMicroelectronics ST19NA18

Read Microcontroller STMicroelectronics ST19NA18 needs to disable the security fuse bits and readout the content from its eeprom and flash memory:

Features summary

Pay TV, Banking and Secure applications

Hardware and dedicated software

Enhanced 8-bit CPU with extended addressing modes

Micromodule Wafer

128 Kbytes User ROM with partitioning

4 Kbytes User RAM with partitioning

18 Kbytes User EEPROM with partitioning,

64 Bytes User OTP and 64 Bytes ST OTP areas:

– Highly reliable CMOS EEPROM submicron technology

– Error Correction Code for single bit fail correction within a byte

– 10-year data retention

– 500,000 Erase/Write cycles endurance

– Erase or Program 1 to 64 Bytes in 1.5 ms

Three 8-bit timers with interrupt capability 3V and 5V supply voltage ranges Power-saving Standby mode

Serial access I/Os, ISO 7816-3 compatible ISO Asynchronous Receiver Transmitter for high speed serial data support

ESD protection greater than 5000 V

AES-128 software library 1088-bit Modular Arithmetic Processor with library support for asymmetrical algorithms

– Fast modular multiplication and squaring using Montgomery method

– Software Crypto libraries in separate ST ROM area for efficient algorithm coding using a set of advanced functions

– Software selectable operand length up to 2176 bits

ISO 3309 CRC calculation block

FIPS 140-2 and AIS31 compliant True Random

Number Generator (TRNG) with two TRNG registers

Unique serial number on each die

High performance provided using high speed internal clock frequency (up to 28 MHz)

Cryptographic performances (1)

– RSA 1024-bit signature with CRT(2): 39 ms

– RSA 1024-bit signature without CRT(2): 130 ms

Security features

– RSA 1024-bit verification (e=’$10001’): 2.4 ms

Very high security features including:

– EEPROM Flash programming

– Clock management

– User ROM protected area

– Code signature capability

– Built-in DFA countermeasures

– Glitch detector

Security firewalls for memories, MAP and

Hardware Security Enhanced DES accelerator with library support for symmetrical algorithms:

– DES, 3 DES computations and CBC mode

– RSA 2048-bit signature with CRT(2): 264 ms

– RSA 2048-bit verification (e=’$10001’): 42 ms

– Triple DES (with enhanced security): 27 µs

– Single DES (with enhanced security): 20 µs