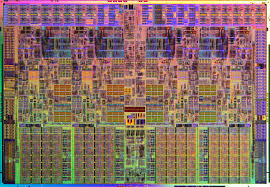

Read Microcontroller Chip Fujitsu MB90F549

Read Microcontroller Chip Fujitsu MB90F549

Embedded PLL clock multiplication circuit, Operating clock (PLL clock) can be selected from: divided-by-2 of oscillation or one to four times the oscillation

Minimum instruction execution time: 62.5 ns (operation at oscillation of 4 MHz, four times the oscillation clock, VCC of 5.0V)

Instruction set to optimize controller applications

Rich data types (bit, byte, word, long word)

Rich addressing mode (23 types)

Enhanced signed multiplication/division instruction and RETI instruction functions

Enhanced precision calculation realized by the 32-bit accumulator

· Instruction set designed for high level language (C language) and multi-task operations

Adoption of system stack pointer

Enhanced pointer indirect instructions

· Program patch function (for two address pointers)

· Enhanced execution speed: 4-byte Instruction queue

· Enhanced interrupt function: 8 levels, 34 factors

· Automatic data transmission function independent of CPU operation

Extended intelligent I/O service function (EI2OS)

· Embedded ROM size and types

Flash ROM: 128 Kbytes / 256 Kbytes

Embedded RAM size: 6 Kbytes / 8 Kbytes (evaluation chip)

· Flash ROM

Supports automatic programming, Embedded Algorithm TM*

Write / Erase / Erase-Suspend / Resume commands

A flag indicating completion of the algorithm

Hard-wired reset vector available in order to point to a fixed boot sector in Flash Memory

Erase can be performed on each block

Block protection with external programming voltage

· Low-power consumption (stand-by) mode

Sleep mode (mode in which CPU operating clock is stopped)

Stop mode (mode in which oscillation is stopped)

CPU intermittent operation mode

Clock mode

· Process

0.5 µm CMOS technology

· I/O port

General-purpose I/O ports: 81 ports

· Timer

Watchdog timer: 1 channel

8/16-bit PPG timer: 8/16-bit × 4 channels

16-bit re-load timer: 2 channels

16-bit free-run timer: 1 channel

Input capture: 8 channels

Output compare: 4 channels

· Extended I/O serial interface: 1 channel

· UART 0

With full-duplex double buffer (8-bit length)

Clock asynchronized or clock synchronized (with start/stop bit) transmission can be selectively used.

With full-duplex double buffer (8-bit length)

Clock asynchronized or clock synchronized serial (extended I/O serial) can be used.

· External interrupt circuit (8 channels)

A module for starting an extended intelligent I/O service (EI2OS) and generating an external interrupt which is triggered by an external input.

· Delayed interrupt generation module

Generates an interrupt request for switching tasks.

· 8/10-bit A/D converter (8 channels)

8/10-bit resolution can be selectively used.

Starting by an external trigger input.

Conversion time: 26.3 µs

· FULL-CAN interfaces

MB90540 series: 2 channel

MB90545 series: 1 channel

Conforming to Version 2.0 Part A and Part B

Flexible message buffering (mailbox and FIFO buffering can be mixed)

· External bus interface: Maximum address space 16 Mbytes

*: Embedded Algorithm is a trade mark of Advanced Micro Devices Inc.

Tags: kırmak mcu binary,kırmak mcu code,kırmak mcu data,kırmak mcu eeprom,kırmak mcu file,kırmak mcu firmware,kırmak mcu heximal,kırmak mcu memory,kırmak mcu program,read microcontroller chip binary code,read microcontroller chip embed firmware,read microcontroller chip encrypt program,read microcontroller chip flash content,read microcontroller chip heximal file,read microcontroller chip protect eeprom,read microcontroller chip software data