MC68HC711PH8 Microcontroller Eprom Software Duplication

MC68HC711PH8 Microcontroller Eprom Software Duplication can effectively help ensure to recover the obselete device which has applied this microcontroller, since this technique can not only make perfect clone unit but also the firmware of original Microcontroller for further research and re-editing:

Enter monitor mode by either

• Executing a software interrupt instruction (SWI) or

• Applying a logic 0 and then a logic 1 to the RST pin.

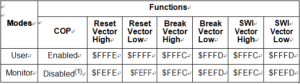

The MCU sends a break signal (10 consecutive logic 0s) to the host computer, indicating that it is ready to receive a command. The break signal also provides a timing reference to allow the host to determine the necessary baud rate by Break Microcontroller MOTOROLA MC68HC811E2FN2. Monitor mode uses alternate vectors for reset, SWI, and break interrupt. The alternate vectors are in the $FE page instead of the $FF page and allow code execution from the internal monitor firmware instead of user code after MCU Recovering.

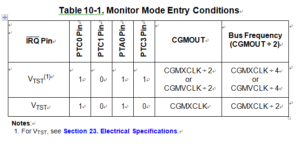

The COP module is disabled in monitor mode as long as VTST (see Section 23. Electrical Specifications) is applied to either the IRQ pin or the RST pin. (See Section 8. System Integration Module (SIM) for more information on modes of operation.)

Holding the PTC3 pin low when entering monitor mode causes a bypass of a divide-by-two stage at the oscillator. The CGMOUT frequency is equal to the CGMXCLK frequency when Attack Motorola MC68HC11A1FN Microcontroller, and the OSC1 input directly generates internal bus clocks. In this case, the OSC1 signal must have a 50% duty cycle at maximum bus frequency.