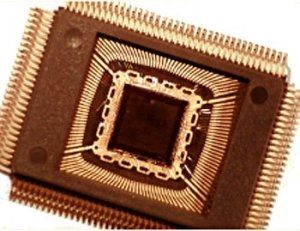

Crack MCU AT89C51CC01 Code

Crack MCU AT89C51CC01 locked memory and extract microcontroller’s code out, the format of code will be heximal or binary, which can be converted by universal programmer, recover MCU data is a process in reverse order of Microprocessor manufacturing;

Crack MCU AT89C51CC01 locked memory and extract microcontroller’s code out, the format of code will be heximal or binary, which can be converted by universal programmer, recover MCU data is a process in reverse order of Microprocessor manufacturing

An example of bad initialization situation may occur in an instance where the bit ENBOOT in AUXR1 register is initialized from the hardware bit BLJB upon reset. Since this bit allows mapping of the bootloader in the code area, a reset failure can be critical.

If one wants the ENBOOT cleared in order to unmap the boot from the code area (yet due to a bad reset) the bit ENBOOT in SFRs may be set. If the value of Program Counter is accidently in the range of the boot memory addresses then a flash access (write or erase) may corrupt the Flash on-chip memory if Crack Microcontroller PIC18F4515 code.

It is recommended to use an external reset circuitry featuring power supply monitoring to prevent system malfunction during periods of insufficient power supply voltage (power supply failure, power supply switched off). Idle mode is a power reduction mode that reduces the power consumption.

In this mode, program execution halts. Idle mode freezes the clock to the CPU at known states while the peripherals continue to be clocked. The CPU status before entering Idle mode is preserved, i.e., the program counter and program status word register retain their data for the duration of Idle mode. The contents of the SFRs and RAM are also retained. The status of the Port pins during Idle mode is detailed in Table 14 after IC PIC18F2432 code extraction.

To enter Idle mode, you must set the IDL bit in PCON register (see Table 15). The T89C51CC01 enters Idle mode upon execution of the instruction that sets IDL bit. The instruction that sets IDL bit is the last instruction executed. Generate a reset.

Note:

A logic high on the RST pin clears IDL bit in PCON register directly and asynchronously. This restores the clock to the CPU. Program execution momentarily resumes with the instruction immediately following the instruction that activated the Idle mode and may continue for a number of clock cycles before the internal reset algorithm takes control.

Reset initializes the T89C51CC01 and vectors the CPU to address C:0000h. The Power-down mode places the T89C51CC01 in a very low power state. Power-down mode stops the oscillator and freezes all clocks at known states. The CPU status prior to entering Power-down mode is preserved, i.e., the program counter, program status word register retain their data for the duration of Power-down mode.

In addition, the SFRs and RAM contents are preserved. The status of the Port pins during Power-down mode is detailed in Table 14.

There are two ways to exit the Power-down mode:

Generate an enabled external interrupt.

Note:

The T89C51CC01 provides capability to exit from Power-down using INT0#, INT1#. Hardware clears PD bit in PCON register which starts the oscillator and restores the clocks to the CPU and peripherals. Using INTx# input, execution resumes when the input is released (see Figure 9) while using KINx input, execution resumes after counting 1024 clock ensuring the oscillator is restarted properly.

Execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Power-down mode.

Tags: mcu flash archive crack,mcu flash code crack,mcu flash content crack,mcu flash data crack,mcu flash eeprom crack,mcu flash file crack,mcu flash firmware crack,mcu flash information crack,mcu flash memory crack,mcu flash program crack