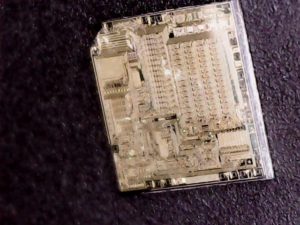

Crack Chip PIC18F458 Program

Crack Chip PIC18F458 tamper resistan system for the purpose of MCU cloning, Program of flash and data of eeprom can be readout from MCU once reverse engineering Microcontroller has been completed;

Crack Chip PIC18F458 tamper resistan system for the purpose of MCU cloning, Program of flash and data of eeprom can be readout from MCU once reverse engineering Microcontroller has been completed

The top of the stack is readable and writable. Three register locations, TOSU, TOSH and TOSL allow access to the contents of the stack location indicated by the STKPTR register. This allows users to implement a software stack, if necessary.

After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU, TOSH and TOSL registers. These values can be placed on a user defined software stack. At return time, the software can replace the TOSU, TOSH and TOSL and do a return.

The user should disable the global interrupt enable bits during this time to prevent inadvertent stack operations. The STKPTR register contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. Register 4-1 shows the STKPTR register.

The value of the Stack Pointer can be through 31. The Stack Pointer increments when values are pushed onto the stack and decrements when values are popped off the stack. At Reset, the Stack Pointer value will be ‘0’. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System for return stack maintenance if decrypt pic mcu 16F59 achiveChip.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit can only be cleared in software or by a POR. The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Over-flow Reset Enable) configuration bit.

Refer to Section 21.0 “Comparator Module” for a description of the device configuration bits. If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to ‘0’ when discover pic mcu pic12f509.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. The 32nd push will overwrite the 31st push (and so on), while STKPTR remains at 31. When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the stack pointer remains at ‘0’. The STKUNF bit will remain set until cleared in software or a POR occurs when Crack Chip.

Since the Top-of-Stack (TOS) is readable and writable, the ability to push values onto the stack and pull values off the stack, without disturbing normal program execution, is a desirable option. To push the current PC value onto the stack, a PUSH instruction can be executed.

This will increment the Stack Pointer and load the current PC value onto the stack. TOSU, TOSH and TOSL can then be modified to place a return address on the stack. The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

These Resets are enabled by programming the STVREN configuration bit. When the STVREN bit is disabled, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a device Reset. When the STVREN bit is enabled, a full or underflow condition will set the appropriate STKFUL or STKUNF bit and then cause a device Reset.

The STKFUL or STKUNF bits are only cleared by the user software or a POR.

Tags: crack chip heximal archive,crack chip heximal code,crack chip heximal content,crack chip heximal data,crack chip heximal eeprom,crack chip heximal file,crack chip heximal firmware,crack chip heximal information,crack chip heximal memory,crack chip heximal program