Clone Microcontroller ATmega644A Heximal

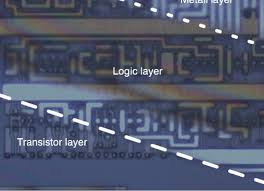

Clone Microcontroller ATmega644A Heximal from the original ATmega644A MCU needs to firstly disable the security fuse bit, and get access to the databus for Program and data extraction;

When the PWM mode is selected, Timer/Counter1 and the Output Compare Register A (OCR1A) form an 8-bit, free-running and glitch-free PWM with outputs on the PB1(OC1A) if pin.

Timer/Counter1 acts as an up-counter, counting up from $00 up to the value specified in the second output compare register OCR1B, and starting from $00 up again.

When the counter value matches the contents of the Output Compare register OCR1A, the PB1(OC1A) pin is set or cleared according to the settings of the COM1A1/COM1A0 bits in the Timer/Counter1 Control Registers TCCR1. Refer to Table 12 for details.

Note that in PWM mode, writing to the Output Compare OCR1A, the data value is first transferred to a temporary location. The value is latched into OCR1A when the Timer/Counter reaches OCR1B.

This prevents the occurrence of odd-length PWM pulses (glitches) in the event of an unsynchronized OCR1A write. See Figure 22 for an example.

During the time between the write and the latch operation, a read from OCR1A will read the contents of the temporary location. This means that the most recently written value always will read out MCU program.

When OCR1A contains $00 or the top value, as specified in OCR1B register, the output PB1(OC1A) is held low or high according to the settings of COM1A1/COM1A0. This is shown in Table 13. The Output Compare Register1 (OCR1B) is an 8-bit read/write register.

This register is used in the PWM mode only, and it limits the top value to which the Timer/Counter1 keeps counting. After reaching OCR1B in PWM mode, the counter starts from $00.

In PWM mode, the Timer Overflow Flag (TOV1) is set as in normal Timer/Counter mode. Timer Overflow Interrupt1 operates exactly as in normal Timer/Counter mode, i.e., it is executed when TOV1 is set provided that Timer Overflow Interrupt and global interrupts are enabled.

This also applies to the Timer Output Compare A flag and interrupt. The frequency of the PWM will be Timer Clock Frequency divided by OCR1B value + 1.

Tags: clone microcontroller dump archive,clone microcontroller dump binary,clone microcontroller dump code,clone microcontroller dump content,clone microcontroller dump data,clone microcontroller dump eeprom,clone microcontroller dump file,clone microcontroller dump firmware,clone microcontroller dump heximal,clone microcontroller dump information,clone microcontroller dump memory,clone microcontroller dump program